FPGA (Field Programmable Gate Array) timing driven layout method with timing constraints

A technology of timing constraints and layout methods, applied in the field of electronics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

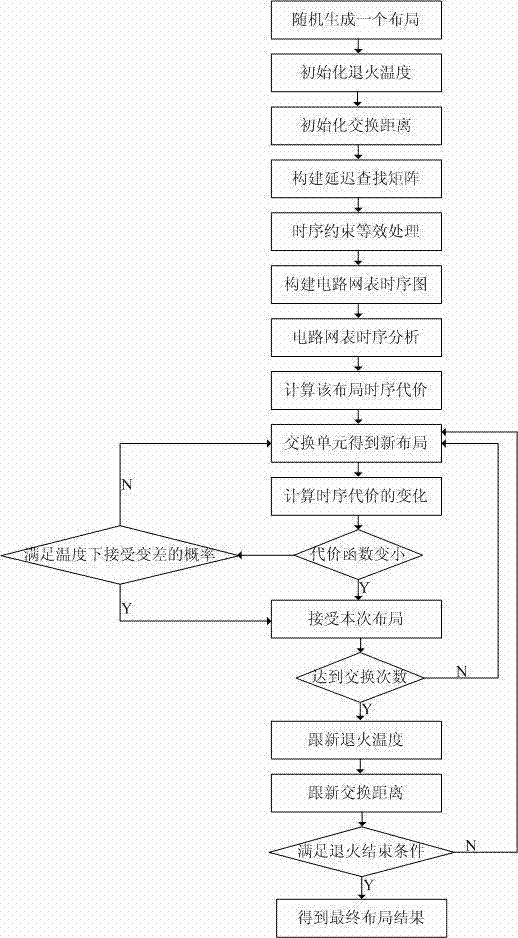

Method used

Image

Examples

Embodiment Construction

[0050] The method of the present invention is specifically described below through a simulation test example: adding minimum clock cycle constraints and input and output delay constraints at the same time.

[0051] (1) Constraint equivalence of the minimum clock period. Timing analysis, find out all the timing paths in the input netlist, and count the delay value of each timing path.

[0052] (2) Equivalent input and output delay constraints. Add the values of the input and output delay constraints to the corresponding timing analysis paths. For the timing path specified by the input delay constraint, the starting point value of the timing path T init Change from the original 0 to the input constraint value C1. Similarly, for the path specified by the output delay constraint, the end point value of the timing path is changed from the original T arrival change to T arrival +C2, C2 is the output delay constraint value of the timing path.

[0053] (3) Perform timing anal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More