Continuous time balance circuit applied to high-speed serial interface

A high-speed serial interface, time equalization technology, applied in the field of data transmission, can solve problems such as large power consumption and area, and achieve the effect of simplifying difficulty and reducing bit error rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

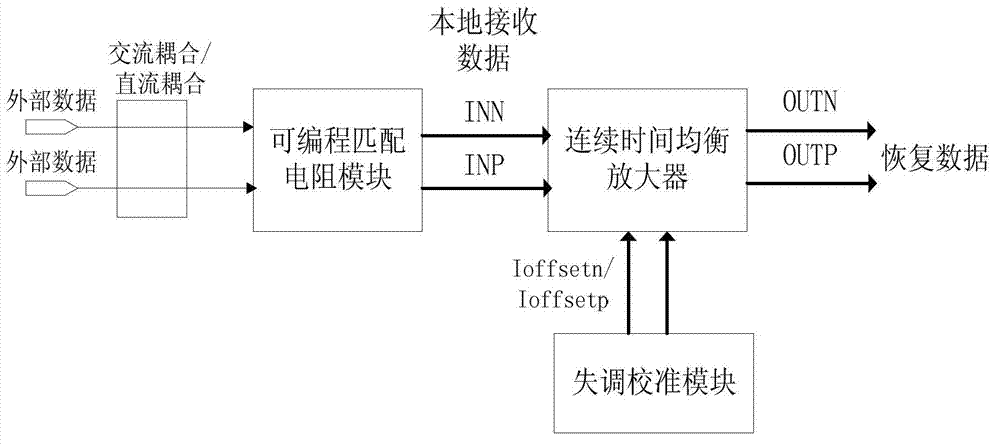

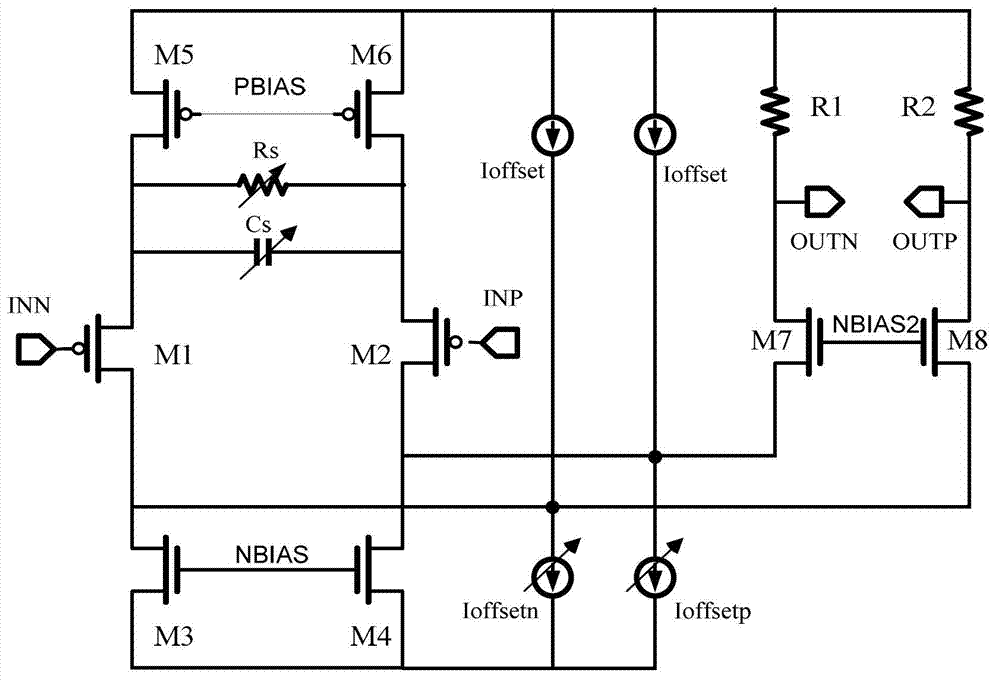

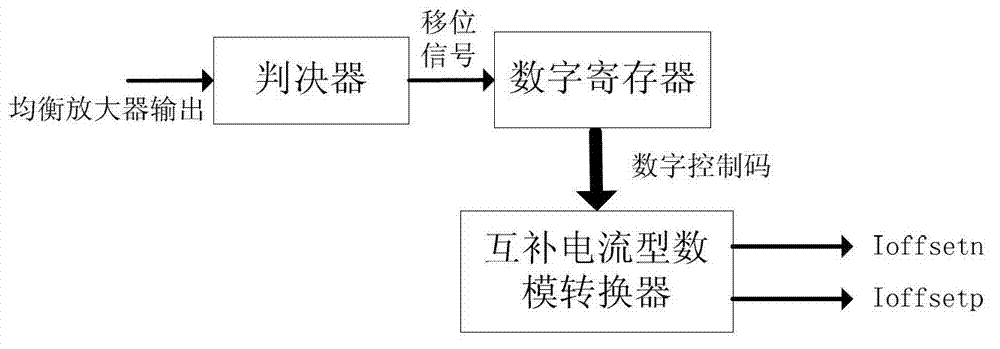

[0019] figure 1 It is a structural schematic diagram of a detunable continuous time equalization circuit applied to the ground implemented by the present invention, and it mainly explains the specific functions and applications of the present invention. figure 1 The continuous-time equalization circuit shown includes a block of programmable matching resistors coupled to ground, continuous-time equalization amplifier and offset calibration block. The way the programmable matching resistance module is coupled to the ground is DC coupling or AC coupling, and its resistance value is adjustable, and the adjustment range is from high resistance to 50 ohm matching resistance. The high-speed data signal outside the chip flows through the programmable matching resistance module through the current, so that the voltage signal INN, INP is gener...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More