Low dropout regulator

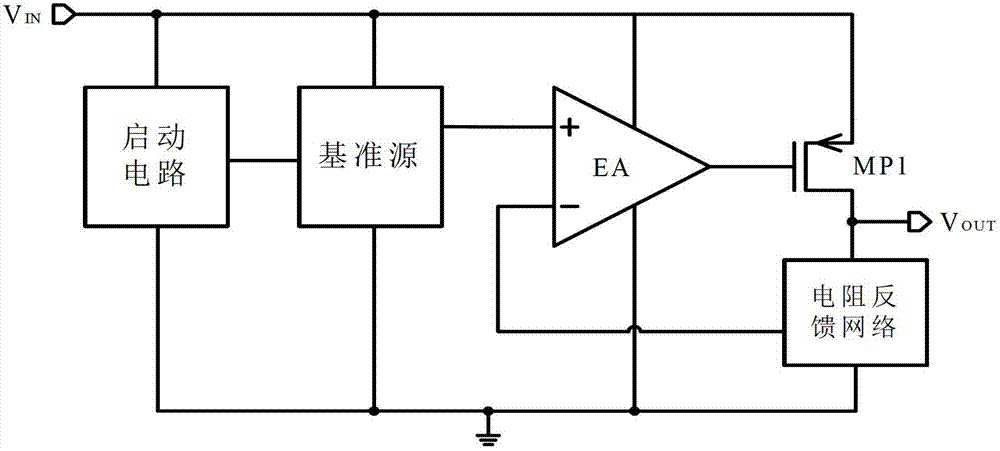

A technology of low-dropout linear and linear voltage regulators, which is applied in the direction of instruments, electrical variable adjustment, control/regulation systems, etc., to enhance pull-up and pull-down capabilities, improve output transient response, and achieve stability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

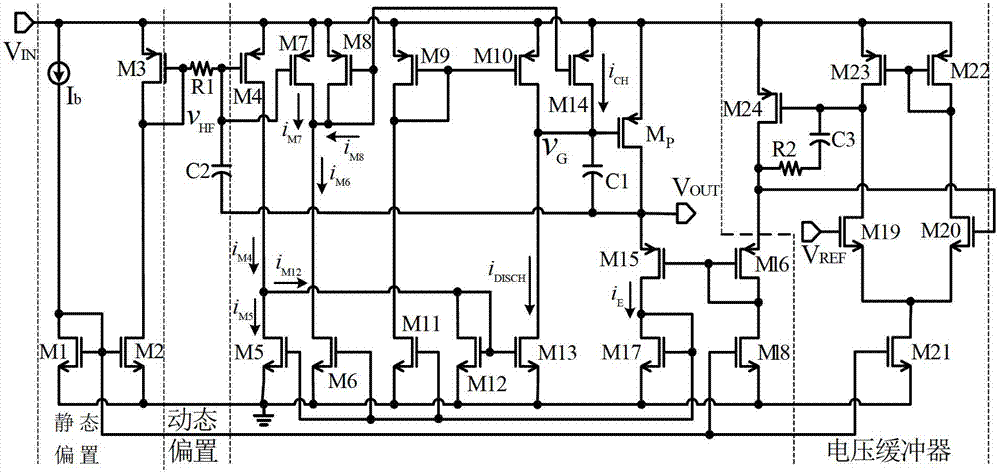

[0024] The structure diagram of the low dropout linear voltage regulator of the present invention is as follows figure 2 As shown, it specifically includes: the current subtraction circuit when the load composed of PMOS transistor M4 and NMOS transistor M5 jumps from light load to heavy load, the fast response path composed of PMOS transistor M7, M8, M14, and NMOS transistor M6, and the PMOS transistor M9 , M10, M15, M16, NMOS tubes M11, M12, M13, M17, M18 composed of a common gate error amplifier and power P tube Mp and compensation capacitor C1.

[0025] As a preferred option, figure 2 A realization form of a bias circuit is given, specifically including: current source Ib, NMOS transistors M1, M2, PMOS transistor M3, resistor R1 and capacitor C2, wherein, current source Ib, NMOS transistors M1, M2, PMOS transistor M3 The static bias is ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Capacitance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More