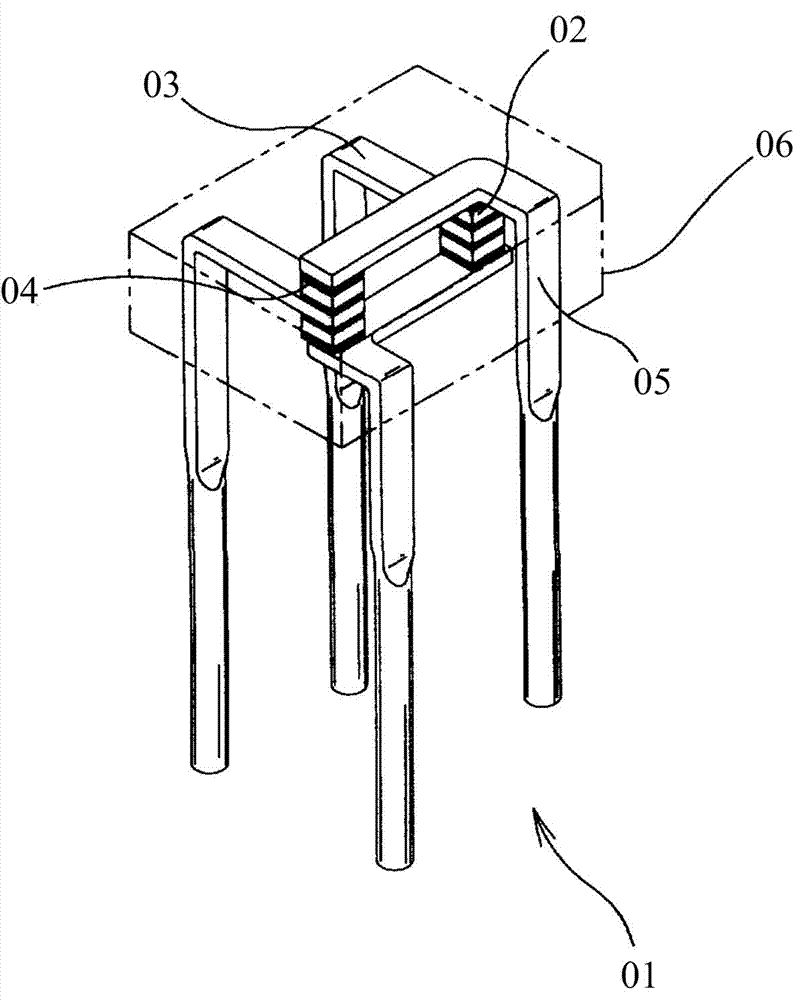

Ultrathin full-wave rectifier

A full-wave rectification, ultra-thin technology, applied in the field of rectifiers, can solve the problems of poor heat dissipation between material grains, electronic circuit power supply failure, large product volume, etc., to achieve high reliability, improve work efficiency, and compact structure. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

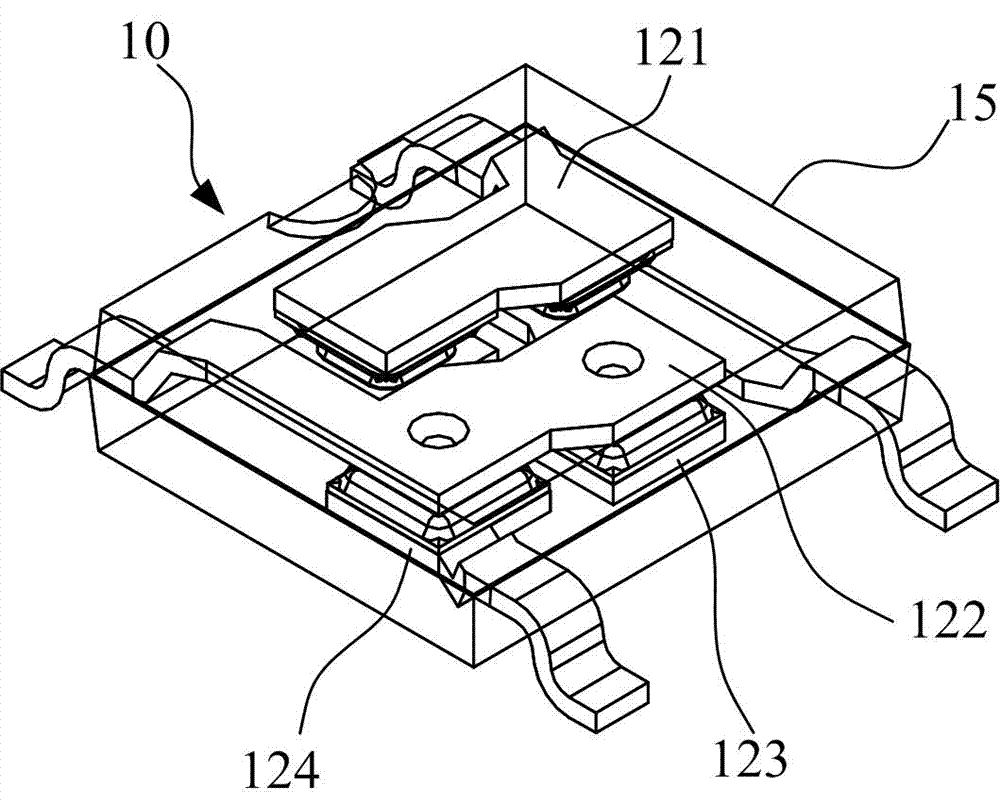

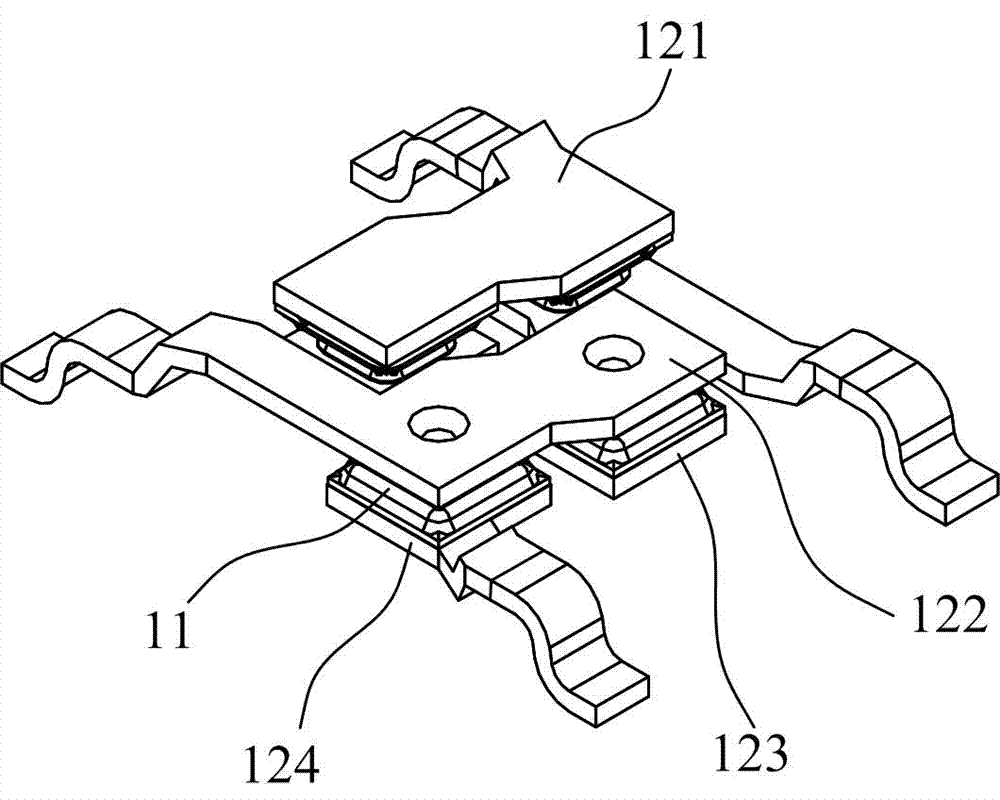

[0030] refer to figure 2 , image 3 , Figure 4 The schematic diagram of the structure of this embodiment is shown.

[0031] In the ultra-thin full-wave rectifier 10 of the embodiment of the present invention, four wafers 11 are included, four electrode contacts 12a, 12b, and the four wafers are arranged in a quadrilateral distribution on a plane, and the polarity of the upper surface of the wafers on each side For reference, the polarity is arranged in order of "different-same-different-same", so that the polarities of the wafers on one pair of sides are the same, and the polarities of the opposite sides are different. In this implementation, it is preferable to arrange the wafers 11 into a parallelogram or a square, and in order to make the structure more compact and reasonable, the present embodiment is preferably a parallelogram distribution, and the parallelogram distribution refers to the formation of a parallelogram distribution on the center line of each wafer, such...

Embodiment 2

[0041] In this embodiment, the FR chip is selected to be assembled into an FR fast rectifier using wafers, so that the reverse recovery time of the ultra-thin full-wave rectifier in this embodiment is between 150 and 1500 nS, and the pitch is set to 2.5 mm, such as Figure 6 The schematic diagram of the structural packaging shown in the figure, other structures are consistent with the description of Embodiment 1, and will not be repeated here.

Embodiment 3

[0043] In this embodiment, the SF chip is selected to be assembled into a SF fast rectifier using wafers, so that the reverse recovery time of the ultra-thin full-wave rectifier in this embodiment is between 15 and 35 nS, and the pitch is set to 4.0 mm. Other structures are the same as The description of Embodiment 1 is consistent, so the description will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More