Low-power-consumption time delay integral type CMOS (Complementary Metal-Oxide-Semiconductor Transistor) image sensor

A technology of time-delay integration and image sensor, which is applied in the field of reducing the power consumption of time-delay integration (TDI) type CMOS image sensor and low power consumption time-delay integration type CMOS image sensor, which can solve the power consumption of analog-to-digital conversion circuit advanced questions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

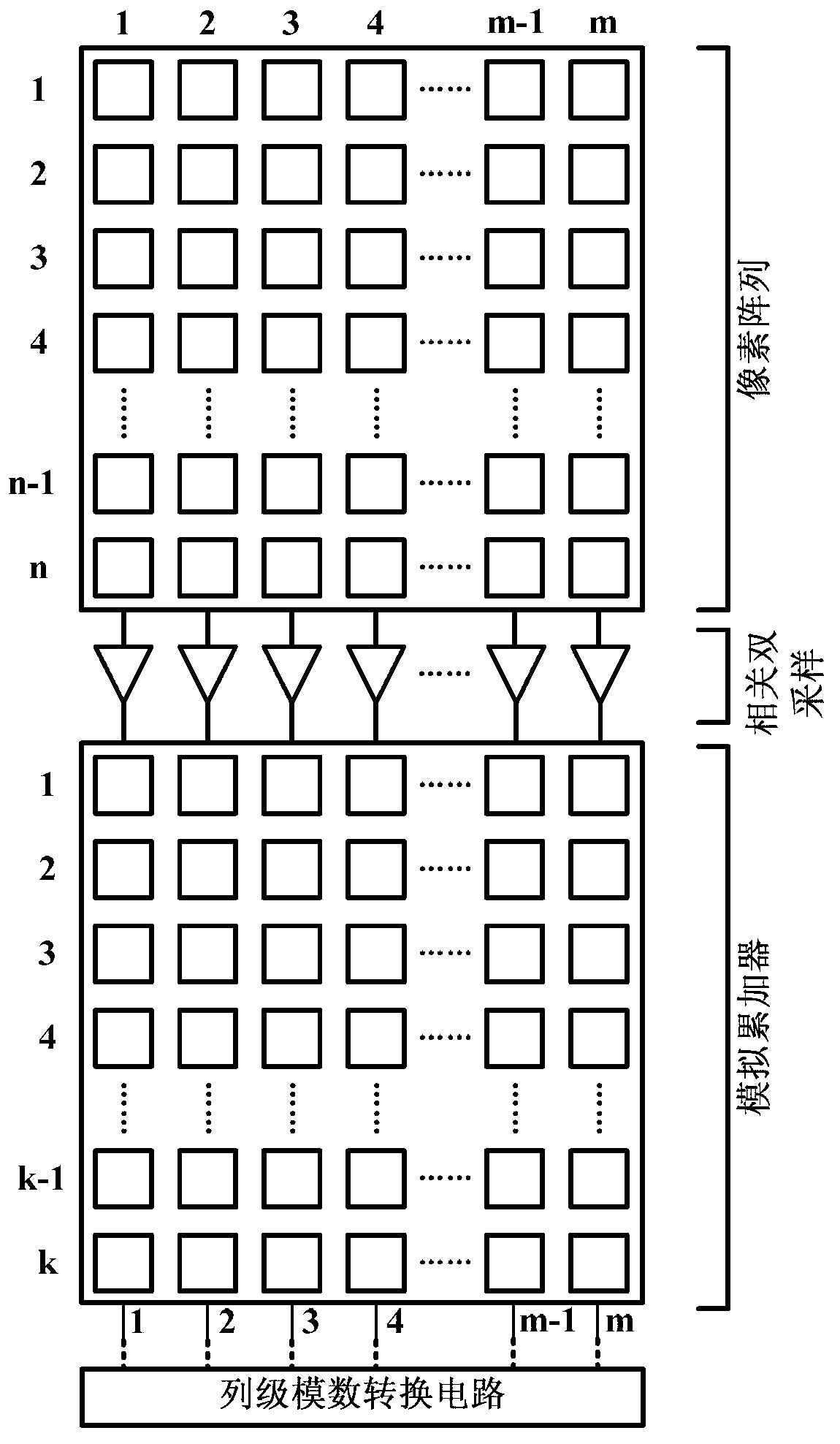

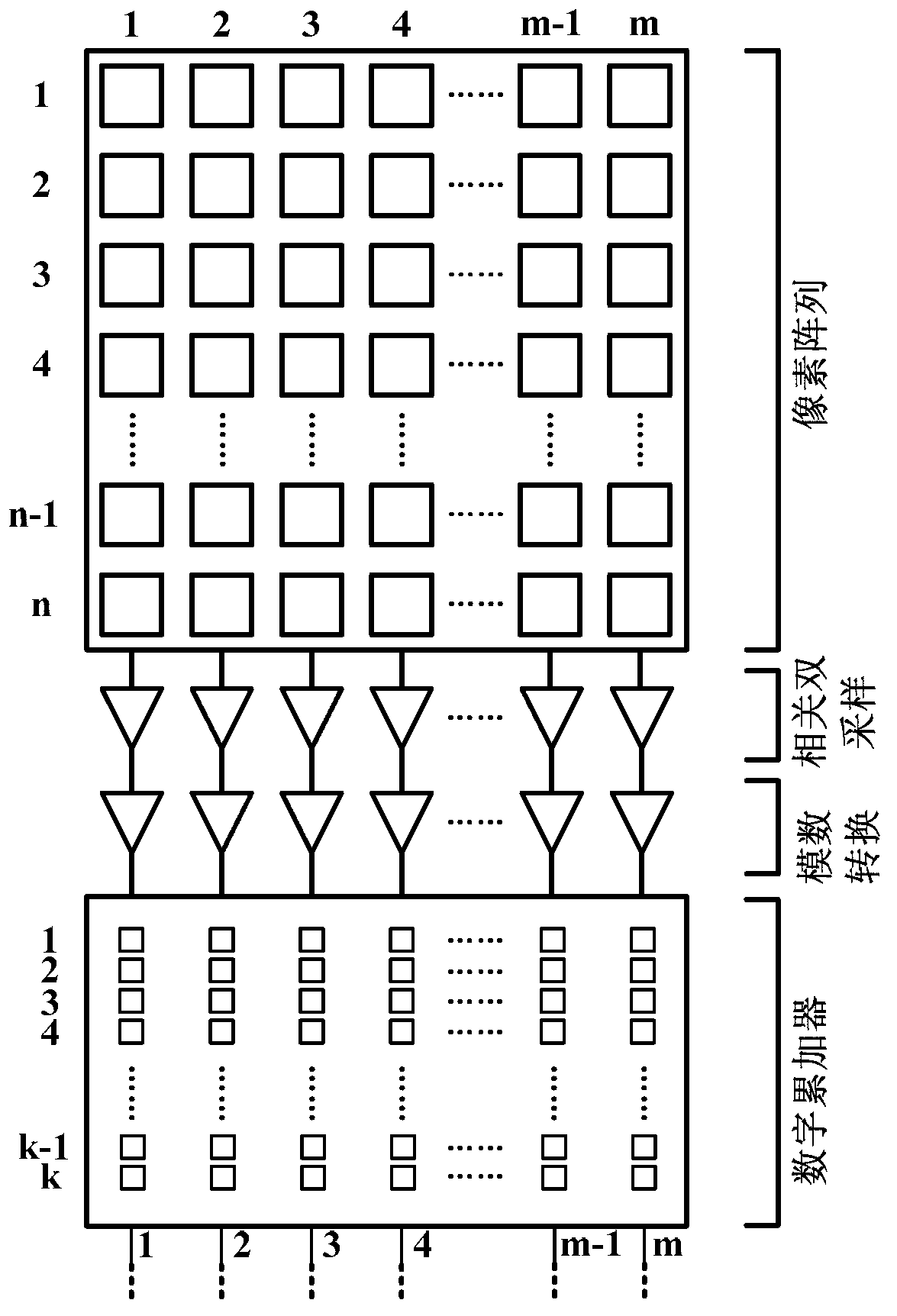

[0030] The present invention proposes an accumulation mode in which the internal charge domain accumulation of the pixel is combined with the external accumulation of the pixel. By reducing the number of external accumulations of the pixel array, the establishment time of the operational amplifier in the external analog domain accumulation mode can be extended, or the external digital domain accumulation can be prolonged. The purpose of the analog-to-digital conversion time in the mode, thereby greatly reducing the power consumption of the entire TDI-CMOS image sensor.

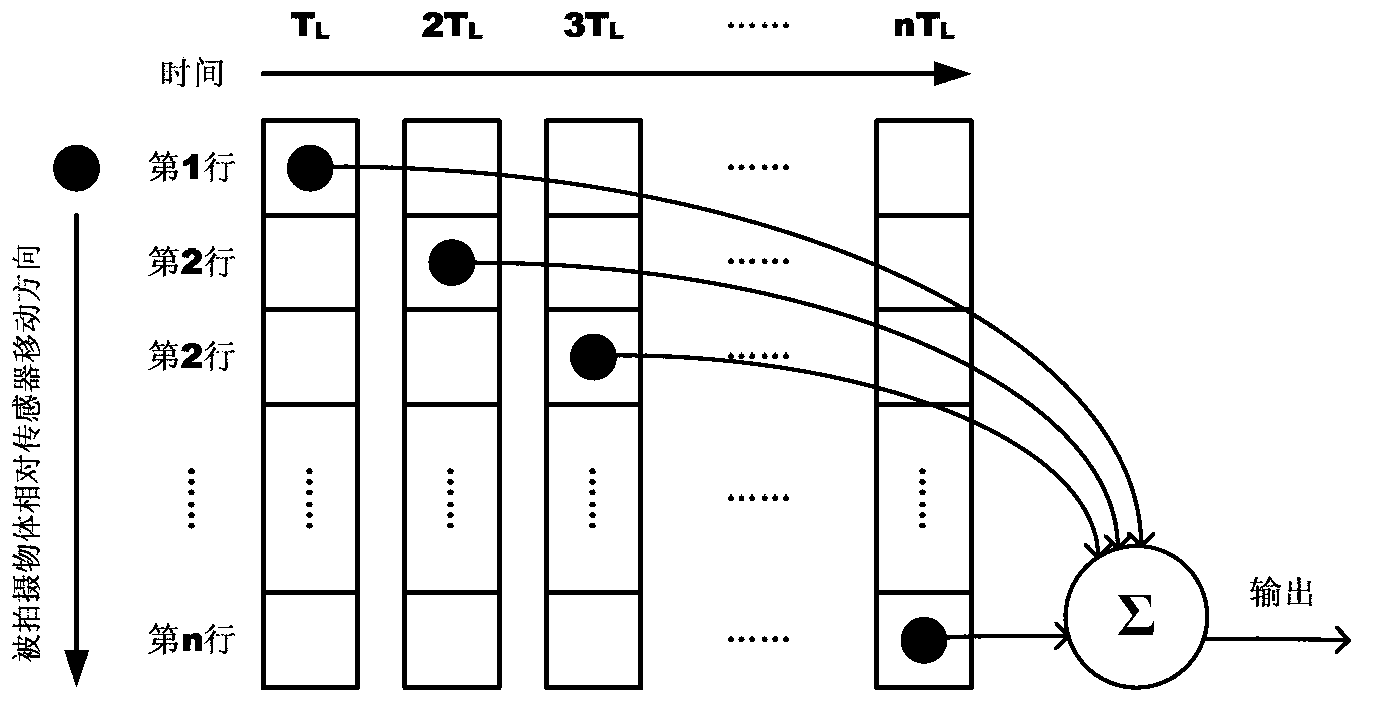

[0031] TDI-type CMOS image sensors mostly adopt a drum-type exposure method, that is, the signals of each row of the pixel array are read out sequentially. For a pixel array with N rows of pixels, during the movement of the sensor relative to the object to be photographed, the object image of the object is sequentially projected into the pixels in the 1st, 2nd, 3rd...N-1, Nth rows. The optional readout sequenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More