Field programmable gate array (FPGA) evaluating method

An evaluation method, the technology of the developer, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of evaluation technology and products, and no third party

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

[0029] The following embodiment is a platform integrating various simulation and testing tools, and the whole process is completed according to the set workflow.

[0030] platform architecture

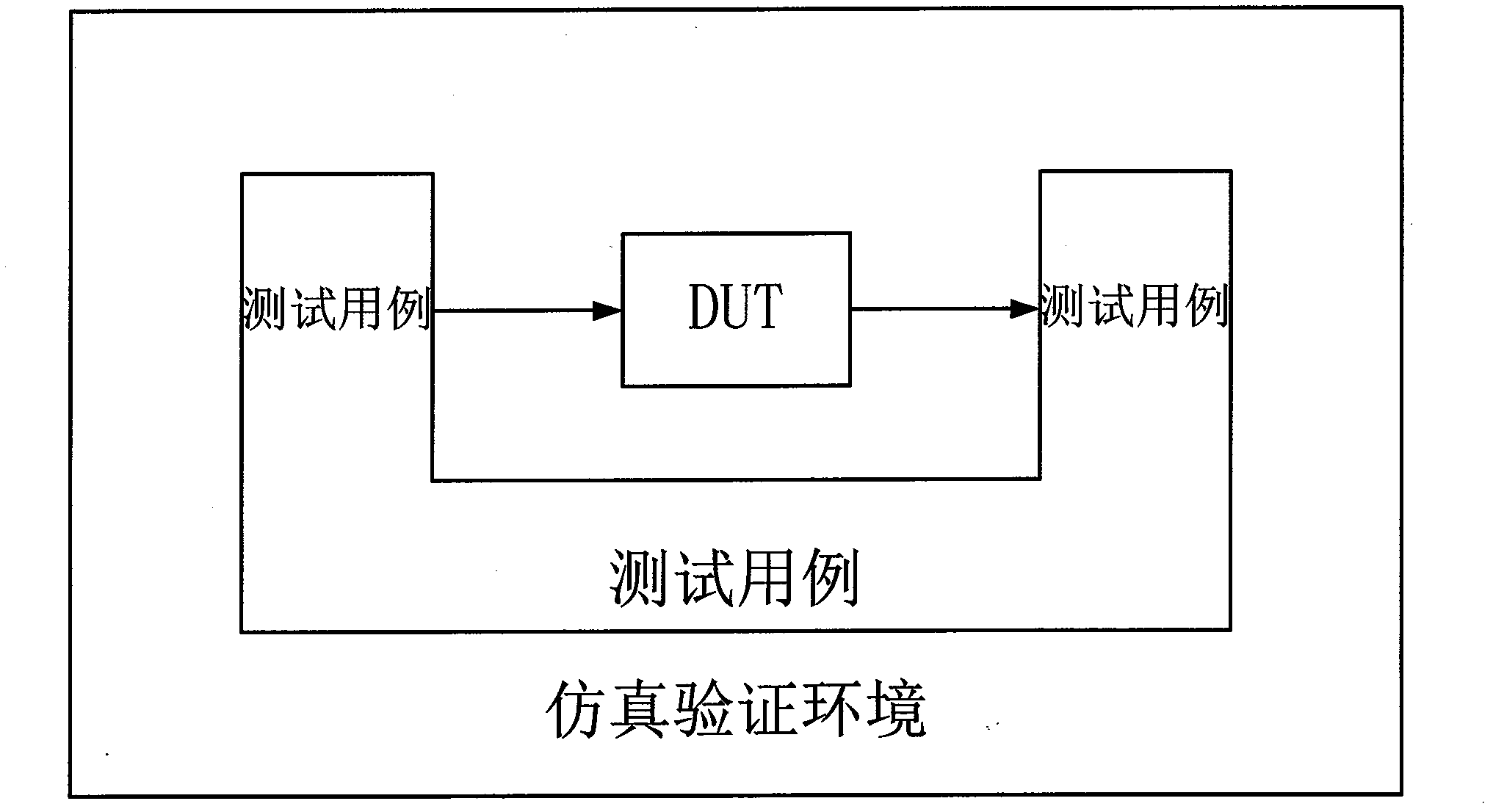

[0031] Such as figure 1 As shown, it includes simulation verification environment, DUT (Device Under Test, test device) and test case (Test Bench), wherein the simulation verification environment includes design environment, triple-mode redundancy tool, operating system and simulation verification tool.

[0032] Work process of the present invention comprises:

[0033] 1. Third-party verification requirements: According to the task book provided by the developer, analyze the FPGA code verification requirements. Output: Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More