Single-instruction-set heterogeneous multi-core system static task scheduling method

A heterogeneous multi-core, task scheduling technology, applied in the direction of multi-programming devices, etc., can solve problems such as unrealistic, inability to guarantee the quality of the solution, complexity and multiple constraints of scheduling problems, etc., to achieve short completion time, initialization efficiency and effective The effect of individual improvement and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

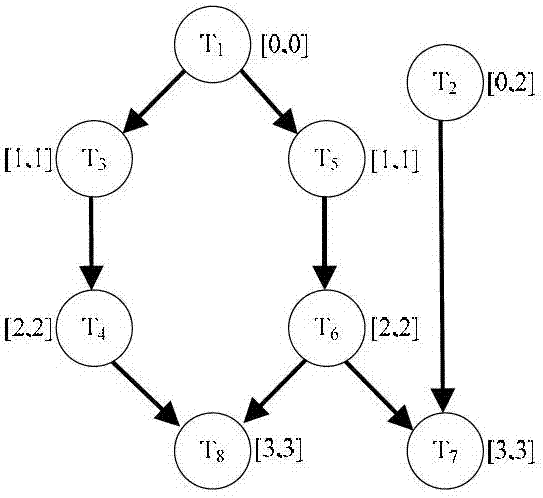

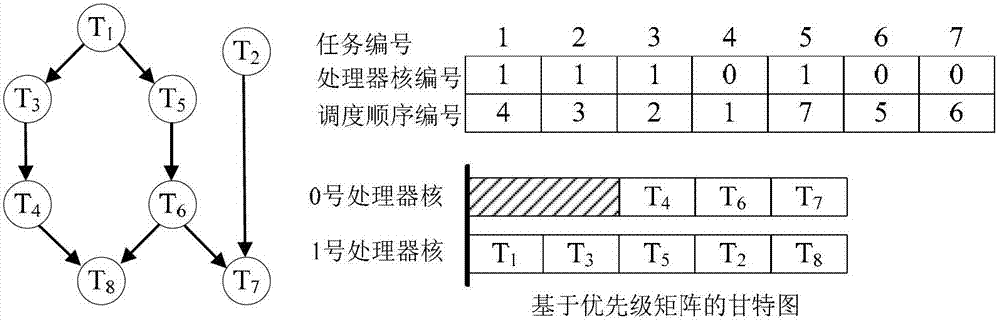

[0084] From figure 1 As shown in the DAG diagram, it can be seen that T 2 The height value is 1, T 5 The height value of is 2, defined according to the height value, T 2 must be at T 5 Before execution, in practice, this constraint is not necessary, from figure 1 It can be seen that T 2 and T 5 There is no constraint relationship between them, as long as T 3 (no matter on which core) the output data after execution is passed to T 5 The processor core where T 5 can be executed, T 2 available at T 5 run after that. In the same way, figure 2 In the DAG graph shown, if height values are used, then T 2 The height value is 0, T 3 with T 5 The height value is 1, then T 2 must be at T 5 done before, in practice, this constraint is also unnecessary, T 2 During execution, T 3 with T 5 is waiting in vain, in order to make way for T on another processor core 4 up and running as early as possible, should allow T 3 before T 2 run. Assuming that the execution time o...

example 2

[0086] In order to simulate and test the effect of multi-objective optimization genetic algorithm when the number of tasks is large, the algorithm is implemented in C language. Randomly generate DAG graphs and task-related attributes of 30 tasks. The processor core configuration is set to two types, 4-core (1 fast core and 3 slow cores) and 8-core (2 fast cores and 6 slow cores), where the main frequency of the fast core is twice that of the slow core. When there is a program running, the power consumption of the processor core is mainly dynamic power consumption, which is related to the main frequency and voltage. The approximate power consumption of the slow core is 2 energy consumption units, and the power consumption of the fast core is 5 energy consumption units. (approximately 2.5 times that of the slow core), assuming that no program is running, the power consumption of the fast core is 1 energy consumption unit, and the power consumption of the slow core is 0.5 energy ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More