Single event upset characteristic testing method for partially triple modular redundancy reinforced SRAM (static random access memory) type FPGA (field programmable gate array)

A technology of single-event flipping and triple-mode redundancy, which is applied in the field of testing single-event flipping characteristics, can solve the problem of increasing the usage of device resources, inability to accurately test the single-event flipping characteristics of SRAM-type FPGAs, and circuit triple-mode redundancy And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

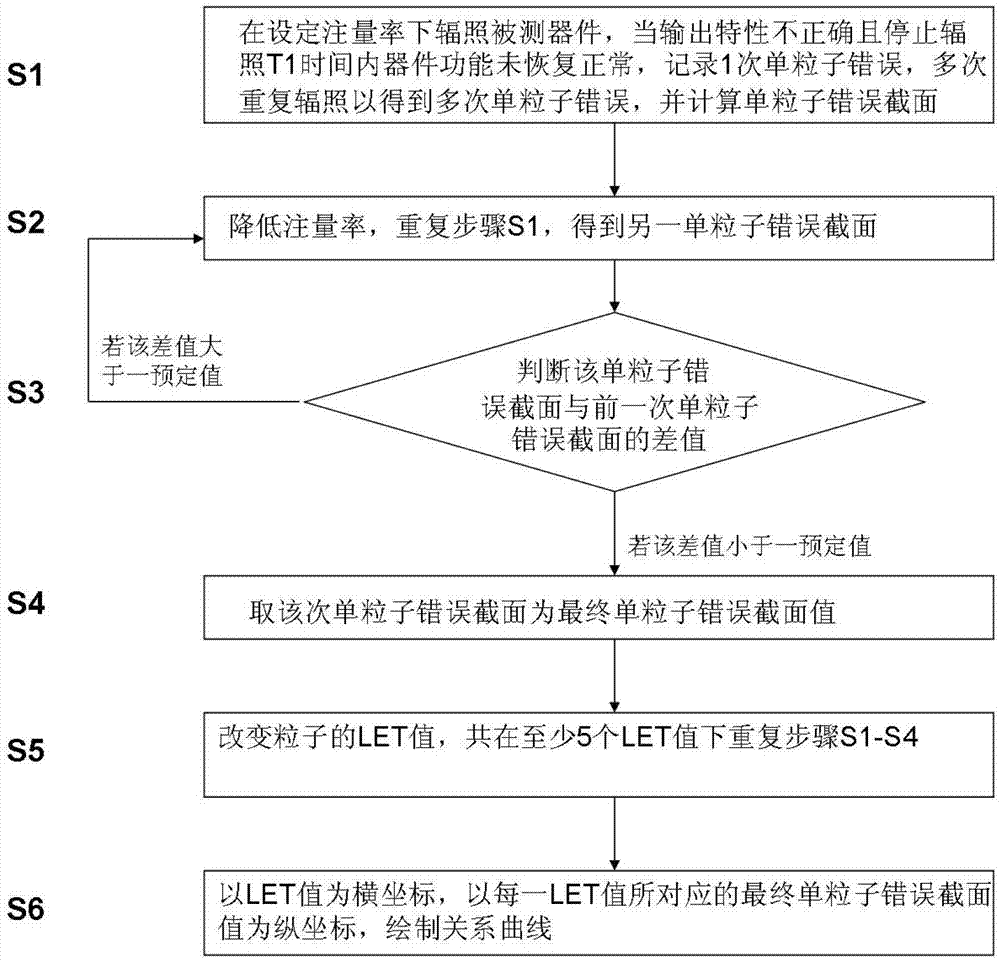

[0019] The present embodiment provides a method for testing the single event flip characteristics of a part of the triple-mode redundant SRAM type FPGA, including:

[0020] 1) Carry out part of the three-mode redundancy reinforcement of the FPGA device under test;

[0021] 2) Use high-energy particles whose LET (energy transfer linear density) value is greater than the switching threshold of the FPGA device, at the set fluence rate (10 2 particles / cm 2 s) irradiate the device under test, and test the output characteristics of the device during the irradiation;

[0022] 3) When the output characteristics of the de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More