Method for reducing area of interconnected input-output pins on stacked chips

A technology of input and output pins, which is applied in the field of reducing the area of interconnected input and output pins on stacked chips, can solve the problems of strong anti-static discharge capability, large driving capability, and large area, so as to reduce chip cost and reduce Chip area, the effect of reducing the area of interconnection input and output pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

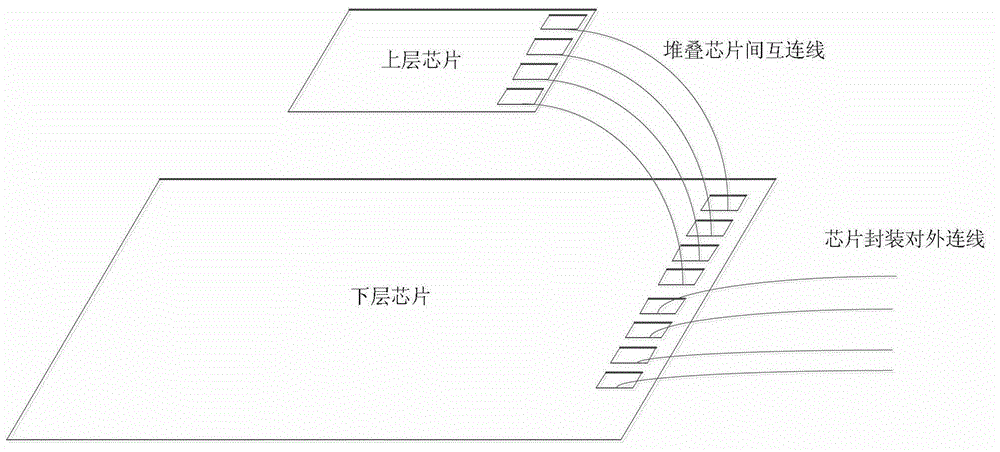

[0027] In this embodiment, by reducing the driving capability of the interconnected input and output pins on the upper and lower stacked chips with the microcontroller standard system bus as the pin interconnection and reducing the performance of its electrostatic discharge protection, thereby reducing its interconnection The size of the output and input pin area, and the size of multiple chips stacked up and down using the microcontroller standard system bus for pin interconnection are further reduced, which further reduces the cost of the SOC chip.

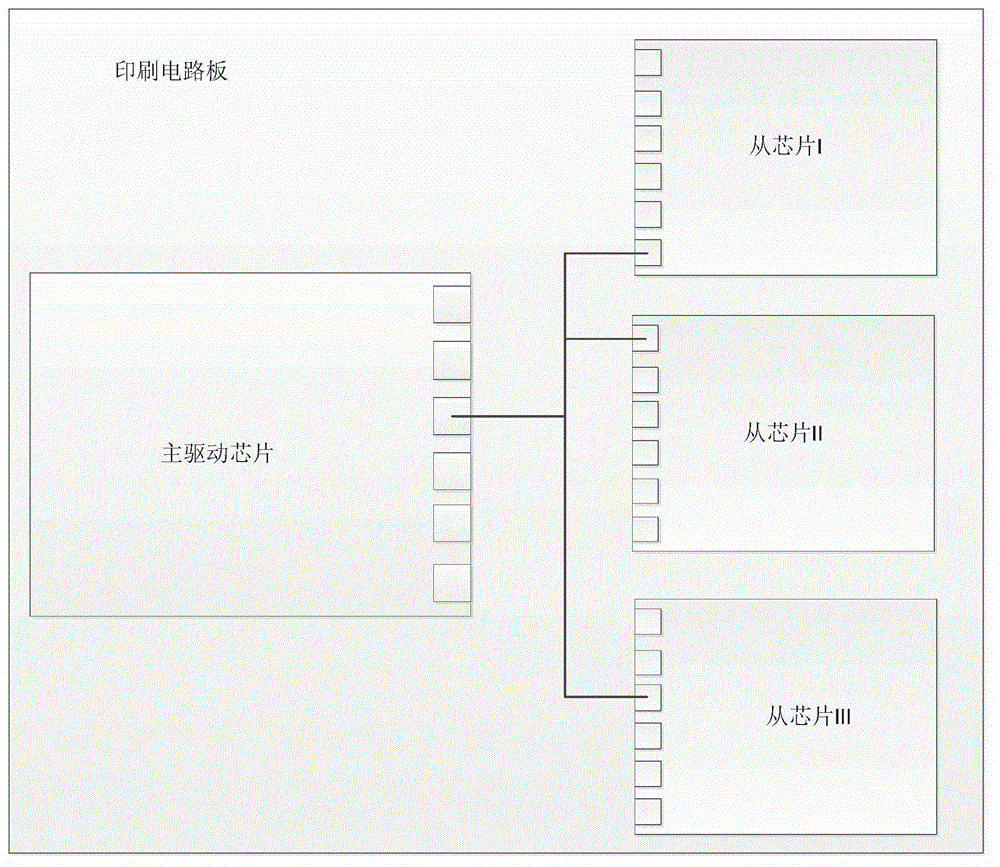

[0028] figure 2 Shown is a generic PCB with a master driver chip and 3 slave chips on top of it. One output pin of the main driver chip is connected to the input pins of the three slave chips to drive three slave chips at the same time, so for the output pin on the main driver chip, its driving capability must be Very large, for example, the driving current is above 20mA. But for multiple chips stacked up and down using the s...

Embodiment 2

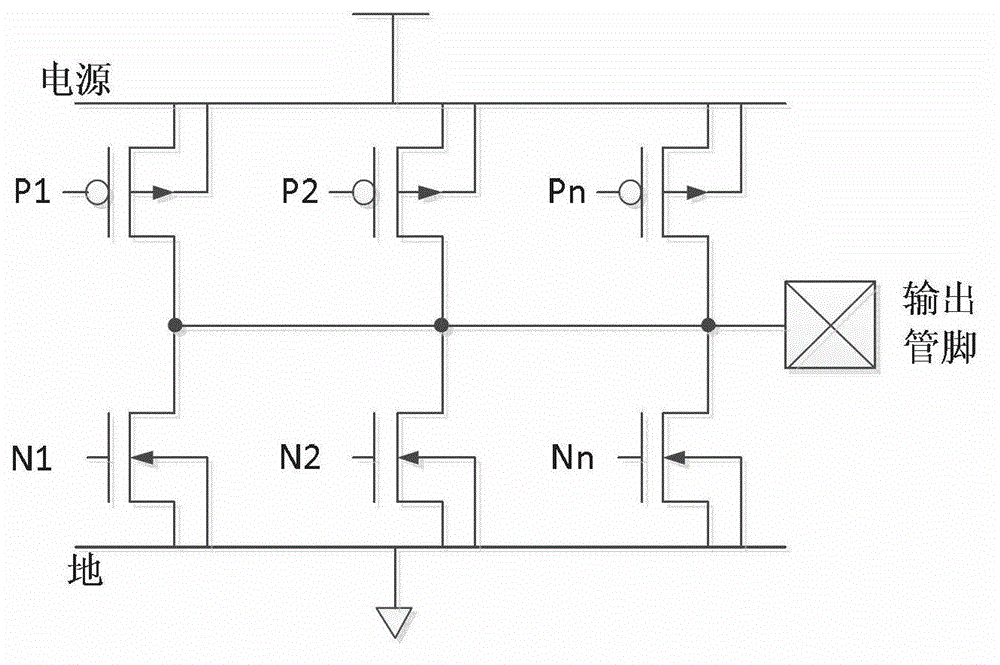

[0032] The interconnection pins of the upper chip in the present invention are not directly connected to the pins of the package shell after the packaging is completed, so the probability of ESD occurring on the upper chip and the requirements for ESD will be reduced. After packaging, the ESD of the whole chip is determined by the ESD performance of the underlying chip. Therefore, on the premise of not reducing the final ESD performance of the chip, the ESD requirements can be reduced by reducing the single transistor size or number of the upper chip ESD transistors (including MOS transistors, diodes or other ESD antistatic structures).

[0033] For example, if the usual HBM 2000V is reduced to HBM 500V, the area of the ESD part of the upper chip can be reduced to a quarter of the original.

[0034] For example, the original ESD transistor that can withstand HBM2000V is composed of 12 NMOS transistors with a width of 30um and a length of 0.45um and 20 PMOS transistors with a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More