Field effect transistor model parameter correction method taking shallow trench isolation into account

A field-effect transistor, model parameter technology, used in electrical digital data processing, special data processing applications, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0064] A specific embodiment of the present invention is given below.

[0065] 1) Use the parasitic parameter extraction tool to extract the STI structure parameters from the input layout, and obtain W=1μm, L=100nm, SA=300nm, SB=300nm, STIW=1μm, STIL=10nm;

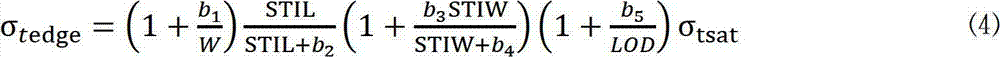

[0066] 2) According to the STI structural parameters W, L, SA, SB, STIW, and STIL, calculate the stress σ along the channel length direction in the MOSFET channel through formulas (1) to (3) l , get σ l =-195.4MPa; Calculate the stress σ along the channel width direction in the MOSFET channel through formula (4) ~ formula (7) t ; get σ t (x)=-79.5exp(-0.0074x)-30.3MPa;

[0067] 3) Calculate the MOSFET model parameter correction amount; specifically include:

[0068] 31) The MOSFET channel stress σ obtained in step 2) l and σ t Bring it into Y.Tan's electron mobility model, and calculate the electron mobility correction amount Δμ n =-5.9%;

[0069] 32) The MOSFET channel stress σ obtained in step 2) l and σ t Brin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More