Preparation method for polycrystalline silicon groove grid and capable of avoiding holes

A trench gate, polysilicon technology, applied in semiconductor devices and other directions, can solve problems such as unfilled voids, and achieve the effect of improving filling capacity and improving device reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

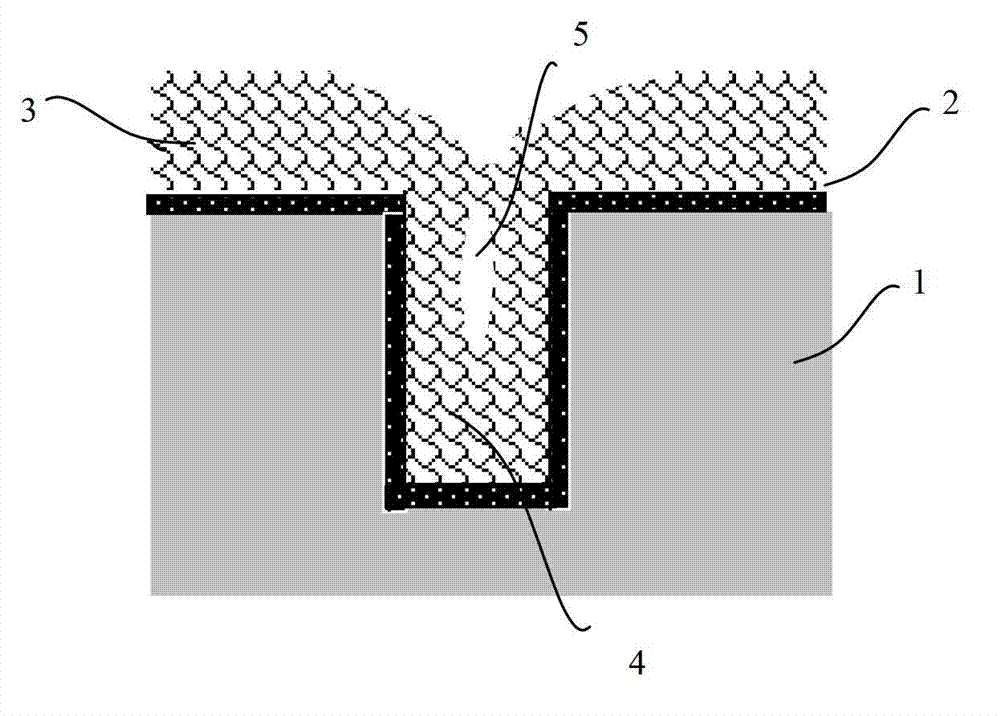

[0023] Such as figure 1 As shown in Fig. 2(a) - Fig. 2(e), the present invention provides a method for preparing a polysilicon trench gate. This preparation method can improve the polysilicon trench gate filling ability, and the preparation process is as follows:

[0024] 1) Defining a deep trench 4 on the silicon substrate 1 by plasma dry etching;

[0025] 2) Grown the gate oxide film 2 on the full silicon wafer in the furnace tube;

[0026] 3) Polysilicon 3 is deposited on the gate oxide film 2. Due to the high aspect ratio of the trench, it is easy to have a cavity 5 on the top of the deep trench 4 during the polysilicon filling process, forming such as figure 1 polysilicon trench gate shown;

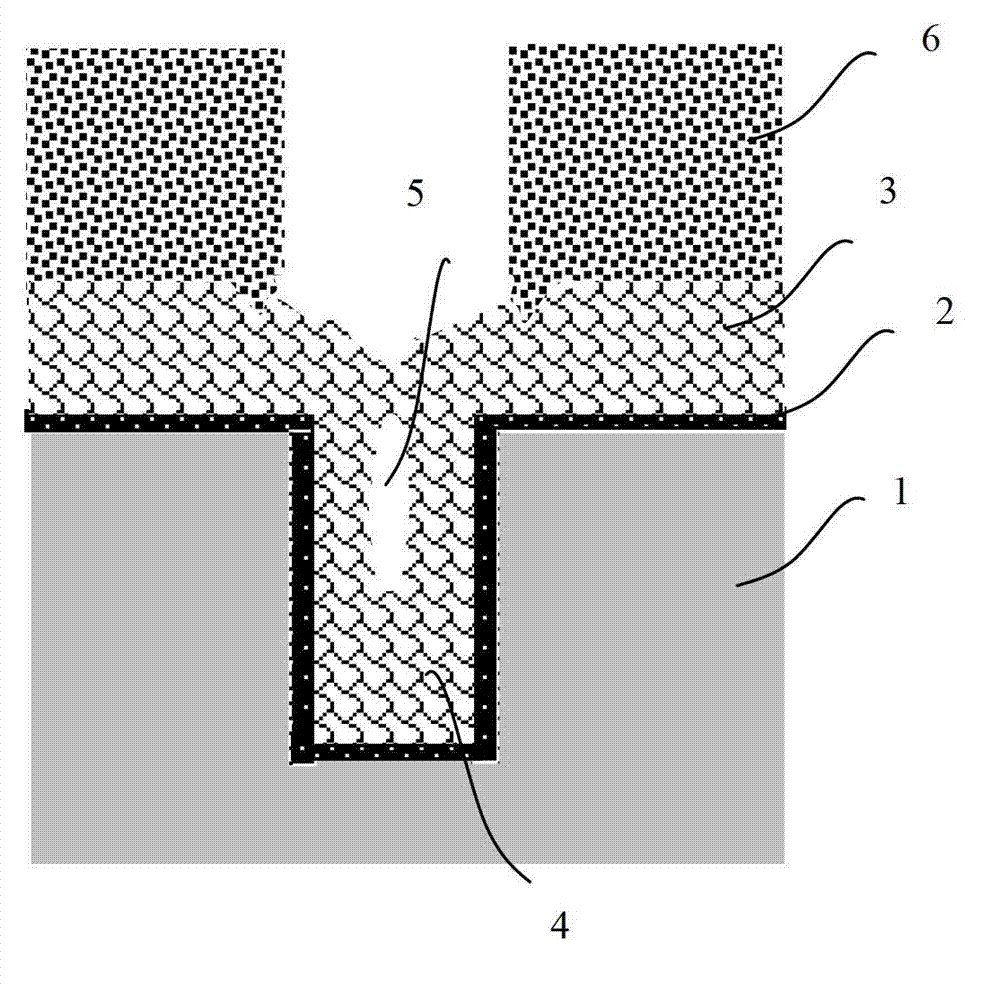

[0027] 4) Coating photoresist 6 and exposing using the deep trench etching layout used in step 1), see Figure 2(a);

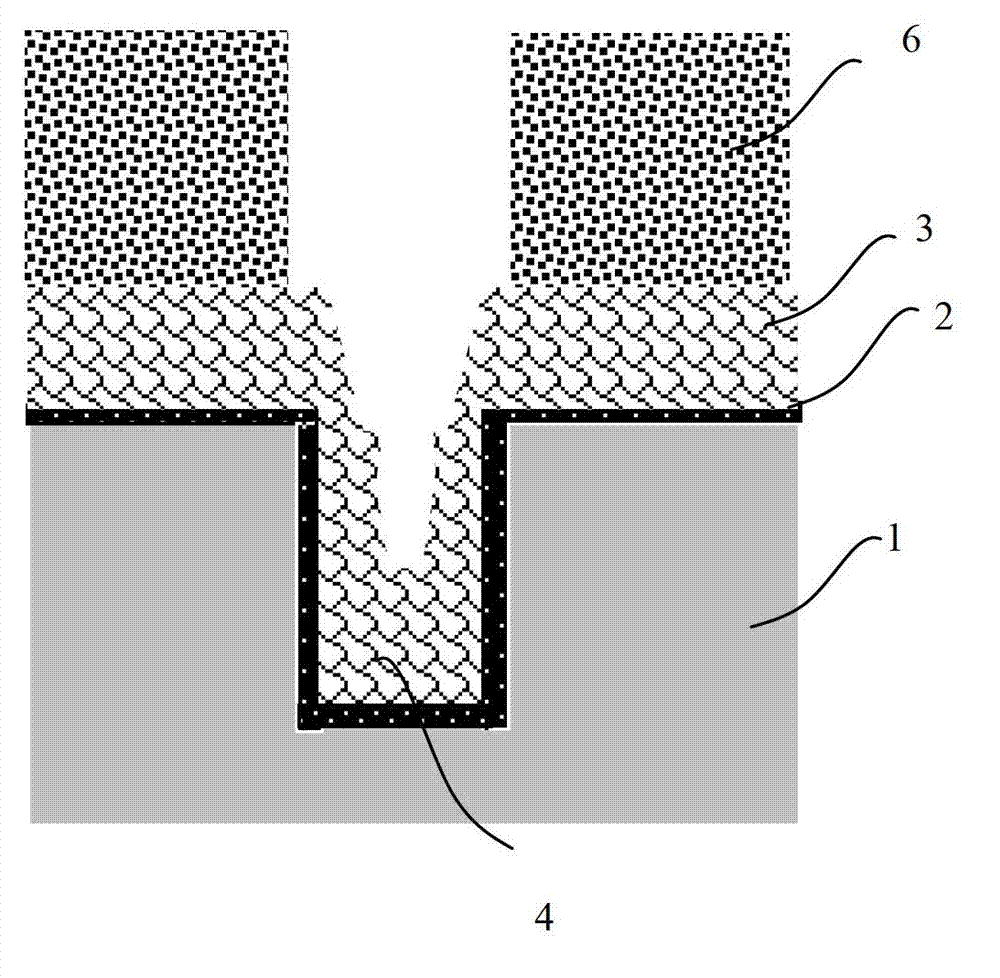

[0028] 5) Using a dry etc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More