Processing method and device of delay between signals

A delay processing and inter-signal technology, applied in the field of communication, can solve problems such as incorrect data demultiplexing results, achieve the effect of solving incorrect data demultiplexing results, high accuracy, and improving the accuracy of data decoding

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

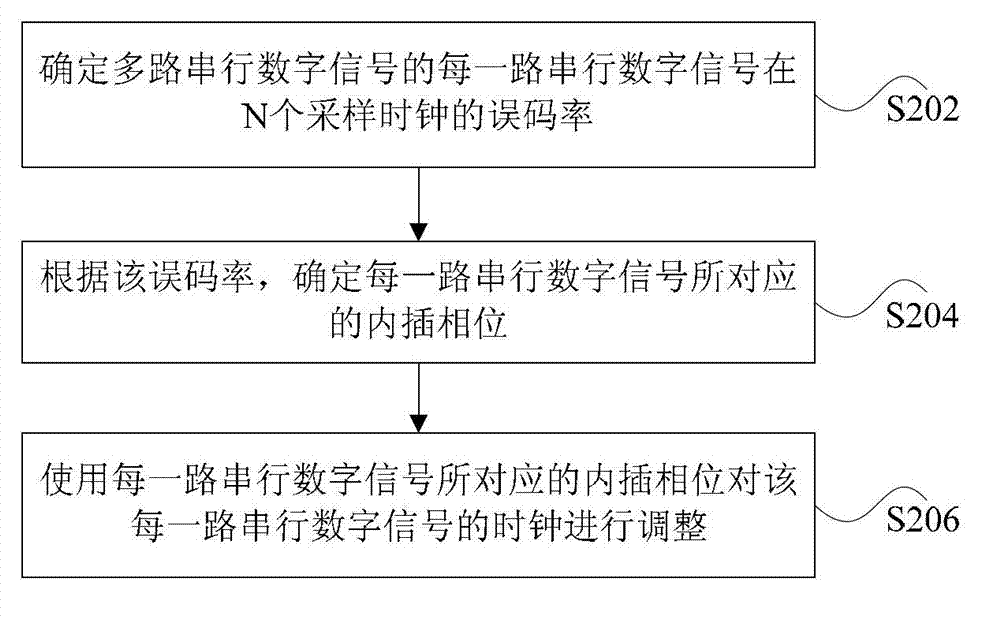

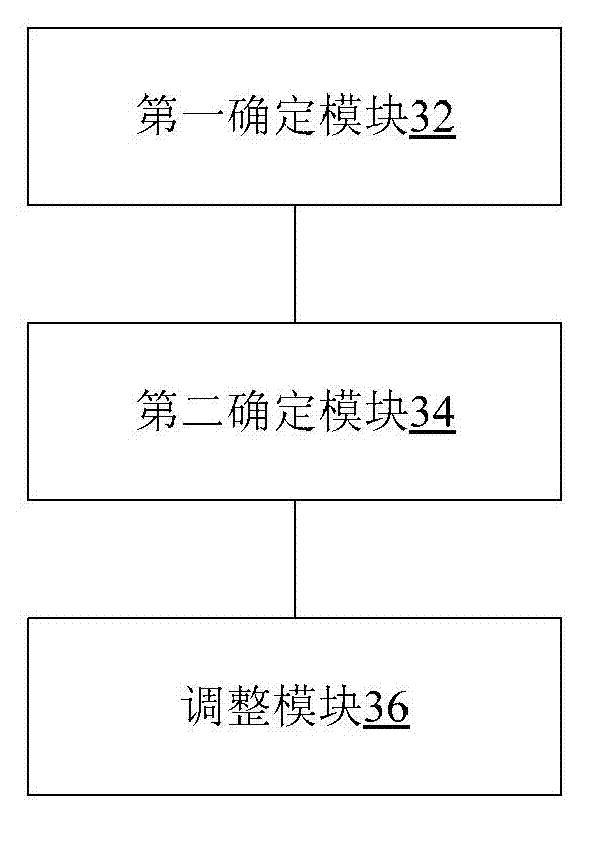

[0051] This preferred embodiment provides a method for adjusting a non-integer multiple delay between symbols, and the method includes the following steps S302 to S310.

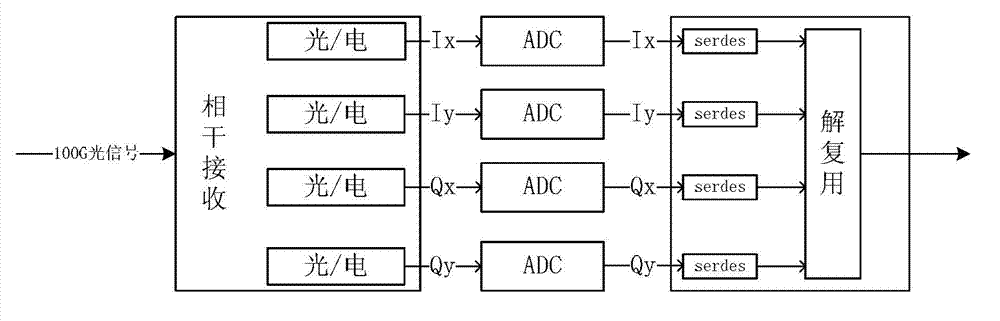

[0052] Step S302: The multiple electrical signals generated through coherent reception are sent to the ADC for sampling, and each electrical signal corresponds to an ADC.

[0053] Step S304: The digital signals sampled by the multi-channel ADCs are sent to the multi-channel serdes for data serial-to-parallel conversion and clock recovery.

[0054] Step S306: Forcibly lock a clock recovery unit (Digital Clock Recovery, CDR for short) of the serdes to a reference clock of the same source as the ADC output data. The CDR of serdes recovers two clocks: a high-speed recovery clock, the clock frequency is half of the serdes rate, which is used to sample the serial input data of the serdes; a low-speed recovery clock, the clock frequency is the same as the rate of the serdes and parallel It is related to the data bi...

Embodiment 2

[0067] This preferred embodiment provides a non-integer multiple delay alignment method for multi-channel data after coherent reception of 100GE services, Figure 8 It is a schematic diagram of a multi-channel data delay alignment method after coherent reception of 100GE services according to an embodiment of the present invention, as shown in Figure 8 As shown, the 100GE signal is sent to the ADC for 1.5 times sampling of the I-channel and Q-channel signals of polarization states X and Y generated by coherent reception, and the signal sampled by each ADC channel is sent to a multi-channel serial-to-parallel converter for conversion and In this process, the CDR of the serdes is forced to lock on the reference clock with the same source as the ADC output data, and the phase interpolation is performed on the high-speed clock recovered by the CDR of each serdes channel, that is, the high-speed clock is adjusted within one clock unit. The sampling position of the row input data, ...

Embodiment 3

[0075] This preferred embodiment provides a method for delay alignment of multi-channel data after coherent reception of OTU4 services, Figure 9 It is a flow chart of the multi-channel data delay alignment method after the OTU4 service is coherently received according to the embodiment of the present invention, as shown in Figure 9 as shown in Figure 9As shown, the OTU4 service signal is sent to the ADC for 1.5-fold sampling of the polarization states X and Y of the I-channel and Q-channel signals generated by coherent reception, and the signal sampled by each ADC channel is sent to a multi-channel serial-to-parallel converter for conversion. And recovery, in this process, the CDR of serdes is forced to lock on the reference clock with the same source as the ADC output data, and the phase interpolation is performed on the high-speed clock recovered by the CDR of each serdes channel, that is, the high-speed clock pair is adjusted within one clock unit The sampling position ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More