Method for making circuit structure

A technology of circuit structure and production method, applied in the direction of printed circuit manufacturing, printed circuit, electrical components, etc., can solve the problems of long electroplating time material cost and time cost, prolong electroplating time, increase production cost, etc., so as to avoid production cost The waste of time and cost, the effect of avoiding environmental pollution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

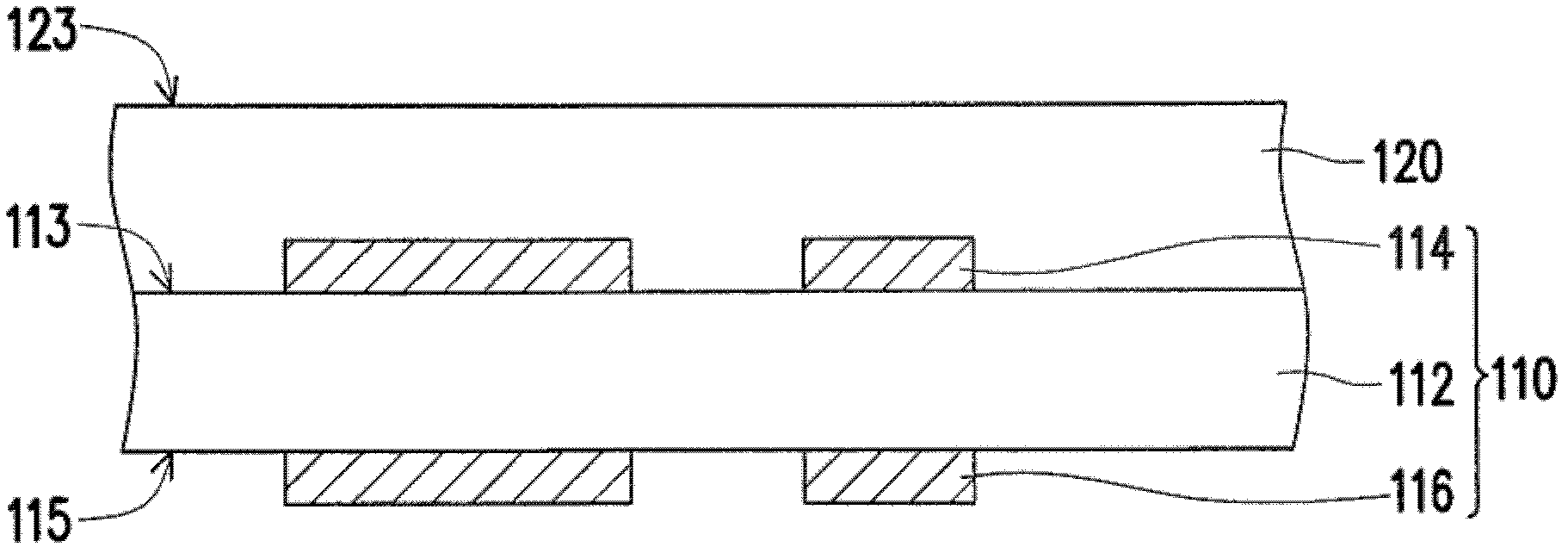

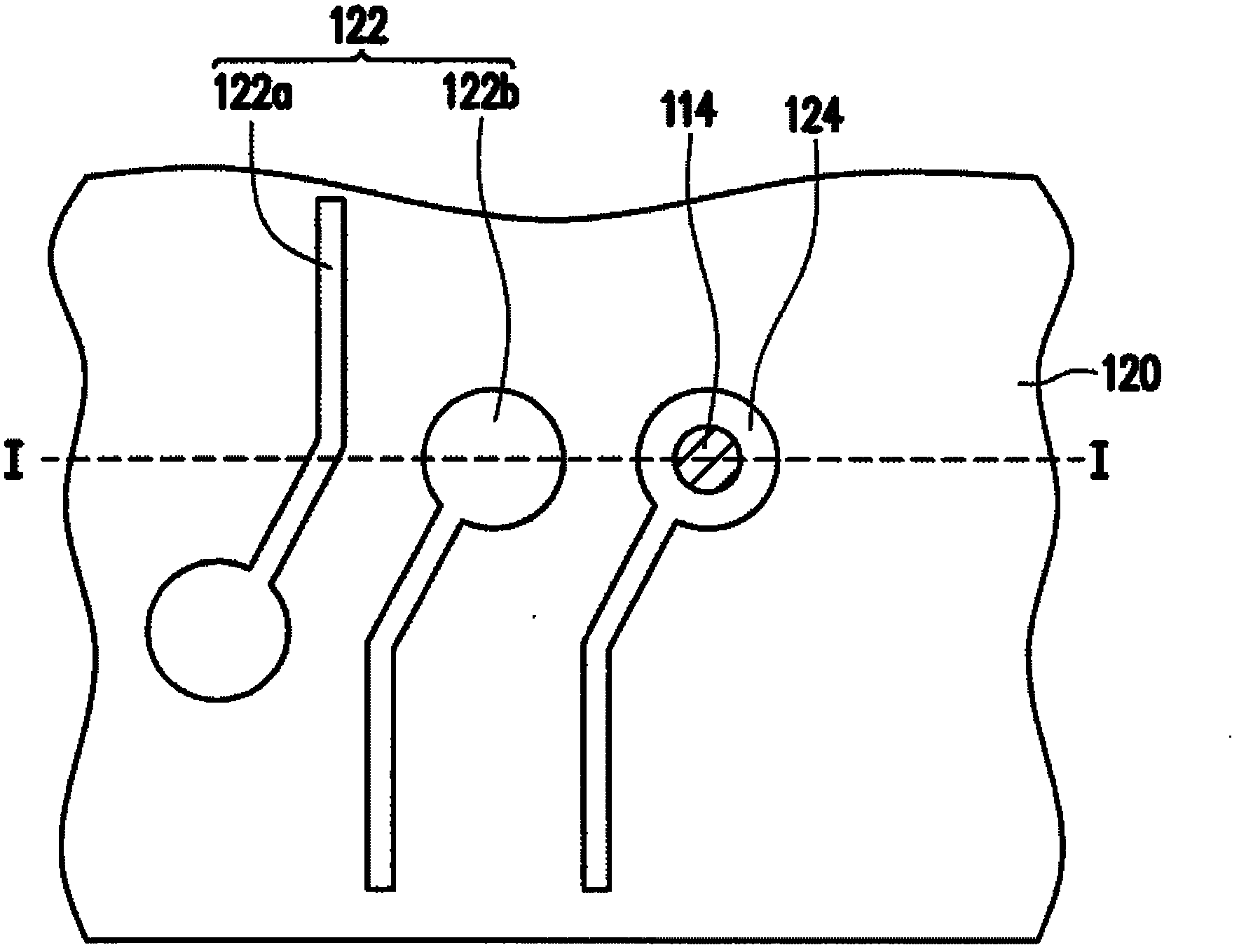

[0033] Figure 1A to Figure 1G It is a schematic top view of a manufacturing method of a circuit structure according to an embodiment of the present invention. Figure 2A to Figure 2G respectively draw along Figure 1A to Figure 1G Schematic cross-section of the line I-I. Please also refer to Figure 1A and Figure 2A According to the manufacturing method of the circuit structure of this embodiment, first, a circuit substrate 110 is provided, wherein the circuit substrate 110 has a first surface 113 and a third surface 115 opposite to each other, a first patterned circuit layer 114 and a The second patterned circuit layer 116 . In this embodiment, the first patterned circuit layer 114 is disposed on the first surface 113 , and the second patterned circuit layer 116 is disposed on the second surface 115 .

[0034] It should be noted that, in other unillustrated embodiments, the first patterned circuit layer 114 and the second patterned circuit layer 116 can also be embedded ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More