Performance testing method of low power consumption chip

A test method and low power consumption technology, which is applied in the field of semiconductor manufacturing, can solve the problems of slow chip performance test speed, etc., and achieve the effect of improving test speed and good compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

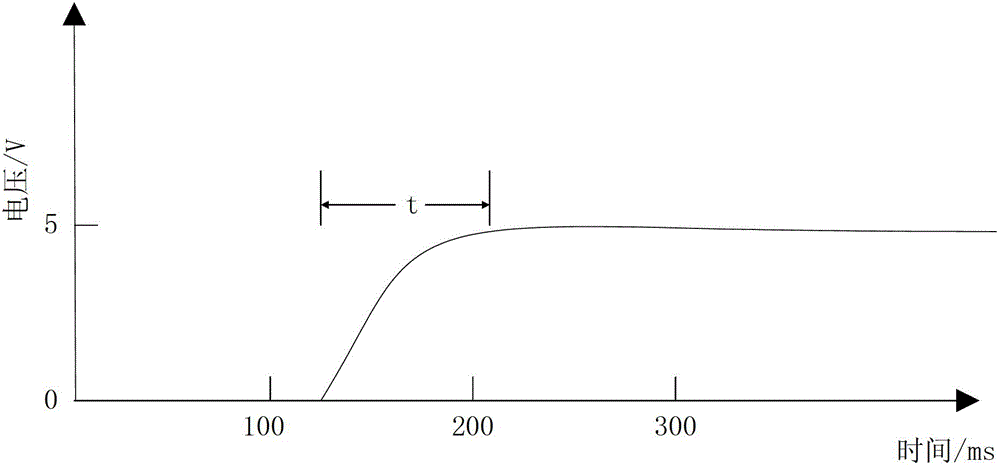

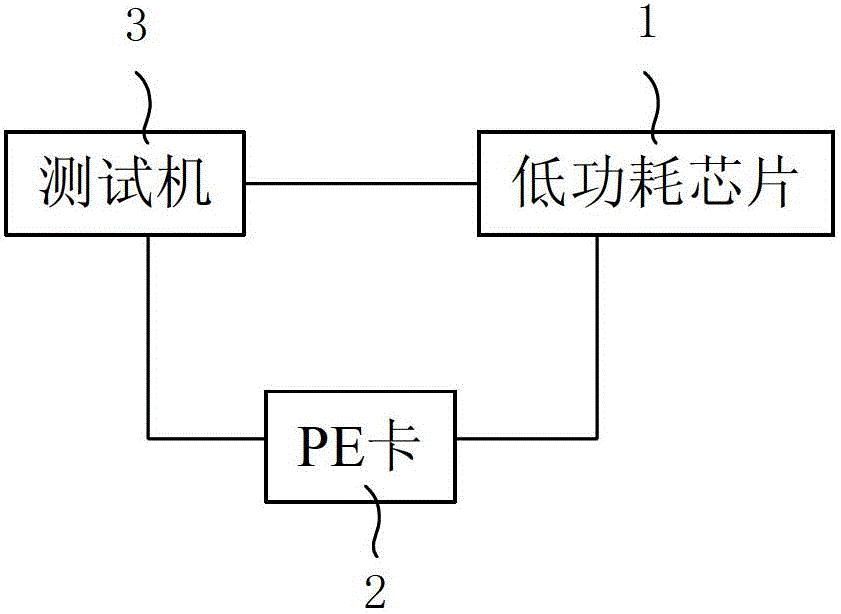

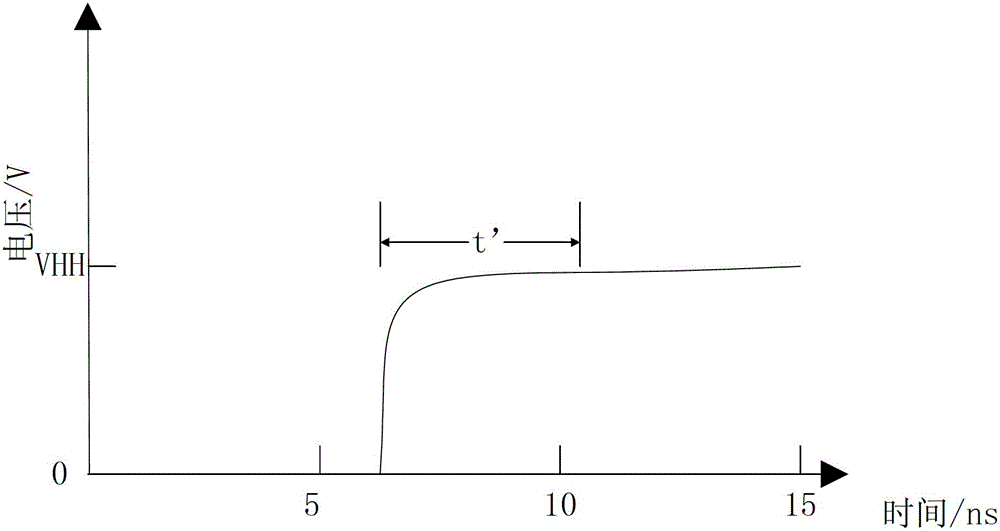

[0028] As mentioned above, in the prior art, the power supply module is used to provide different power supply voltages for performance testing of the chip. The rising edge time of the power supply module is relatively long, usually tens to hundreds of microseconds, thus causing chip performance The test rate is slower. In view of the above problems, the present invention adopts a power supply mode of high and low levels, and the rising edge time of the high level in the high and low levels is relatively short, generally several nanoseconds to tens of nanoseconds, thus, the test rate can be improved, and for this The power supply mode of high and low levels generally provides the characteristics of small working current, and the technical solution of the present invention is aimed at the performance test of low power consumption chips.

[0029] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More