Method for reducing silicon etching loading effect

A technology of etching load and effect, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of improving silicon etching load effect and solving manufacturing process problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

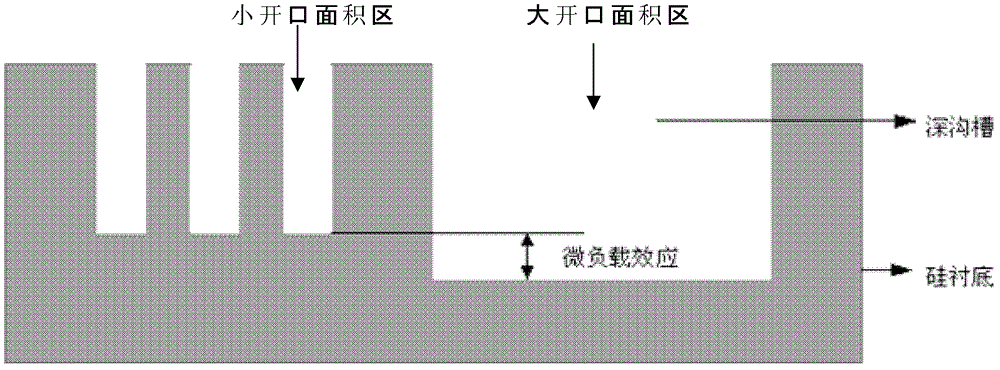

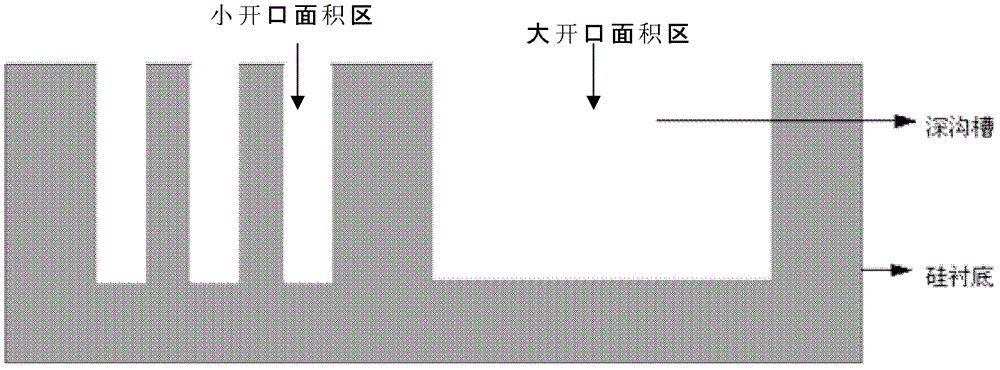

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Embodiment 1 of the present invention mainly comprises following specific steps:

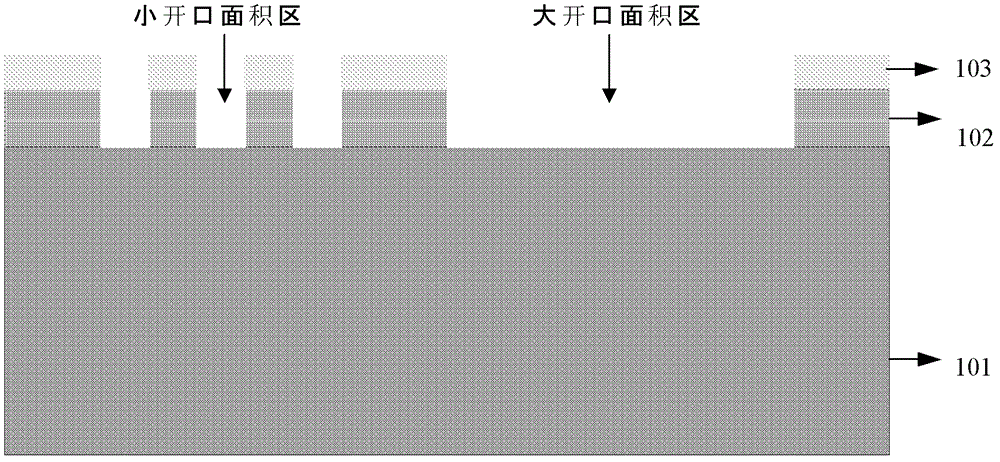

[0045] 1. If image 3 As shown, one or more dielectric films are deposited on the silicon substrate 101 as the hard mask layer 102, for example, a layer of dielectric film (such as an oxide film) can be deposited on the silicon substrate 101 as the hard mask layer 102, or An oxide film with a thickness of 125 angstroms and a SiN film with a thickness of 1500 angstroms are deposited on the silicon substrate 101 as the hard mask layer 102, because the oxide film acts as a buffer layer between the silicon substrate 101 and the SiN film, so image 3Only one film (ie, the hard mask layer 102, which includes an oxide film and a SiN film) is depicted in the figure. Then, the first photoresist 103 is coated, developed, and a pattern of the hard mask layer is formed, including a large opening area area and a small opening area area. The hard mask layer 102 is then etched, stopping on top of the ...

Embodiment 2

[0051] In order to achieve the purpose of removing the oxide film in the large opening area region and retaining the oxide film in the small opening area region, there is another alternative solution, that is, Example 2. Embodiment 2 mainly includes the following concrete steps:

[0052] 1. As Figure 5 As shown, one or more dielectric films are deposited on the silicon substrate 101 as the hard mask layer 102. For example, a dielectric film (such as an oxide film) may be deposited on the silicon substrate 101 as the hard mask layer 102, or A layer of oxide film with a thickness of 125 angstroms and a SiN film with a thickness of 1500 angstroms are deposited on the silicon substrate 101 as the hard mask layer 102, because the role of the oxide film is to serve as a buffer layer between the silicon substrate 101 and the SiN film, so image 3 Only one layer of film (ie hard mask layer 102, which includes oxide film and SiN film) is drawn in the middle; then the first photoresis...

Embodiment 3

[0057] Embodiment 3 of the present invention mainly includes the following specific steps:

[0058] 1. As image 3 As shown, one or more dielectric films are deposited on the silicon substrate 101 as the hard mask layer 102. For example, a dielectric film (such as an oxide film) may be deposited on the silicon substrate 101 as the hard mask layer 102, or A layer of oxide film with a thickness of 125 angstroms and a SiN film with a thickness of 1500 angstroms are deposited on the silicon substrate 101 as the hard mask layer 102, because the role of the oxide film is to serve as a buffer layer between the silicon substrate 101 and the SiN film, so image 3 Only one film (ie, the hard mask layer 102, which includes an oxide film and a SiN film) is depicted in the figure. Then, the first photoresist 103 is coated and developed to form a pattern of the hard mask layer, including a large opening area area and a small opening area area. The hard mask layer 102 is then etched, stopp...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More