Double data rate (DDR) 2 synchronous dynamic random access memory (SDRAM) controller

A technology for controllers and control registers, which is applied in the direction of instruments, electrical digital data processing, etc., and can solve the problems of not realizing the reordering function of read/write request commands, reducing bandwidth utilization, and low bandwidth utilization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

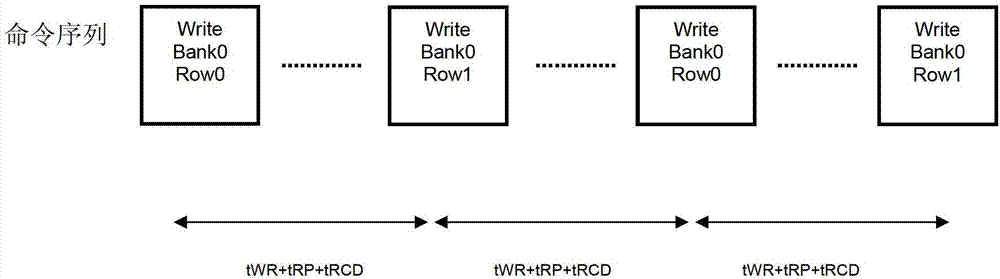

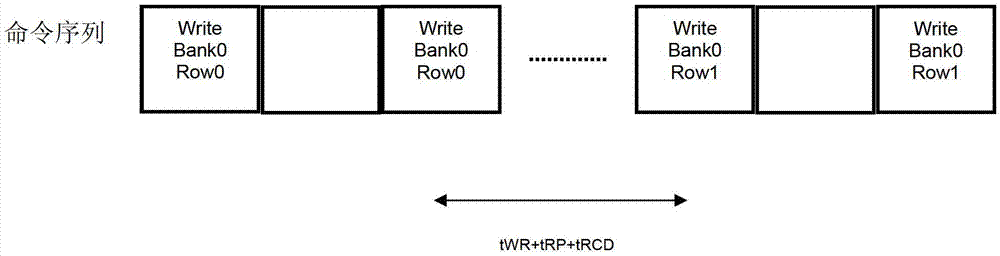

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

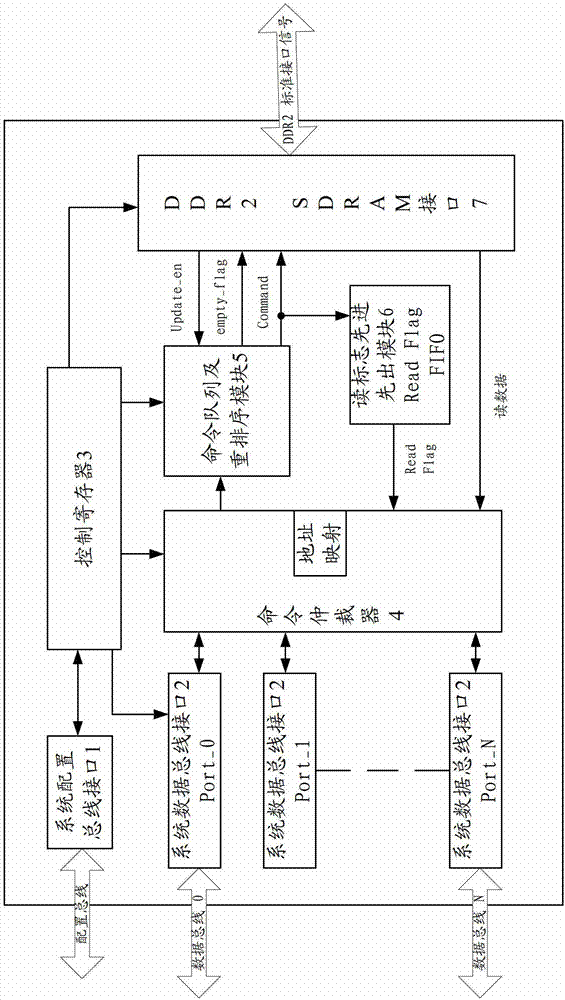

[0087] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0088] Such as image 3 As shown, the present invention provides a DDR2 SDRAM controller, including a system configuration bus interface 1, one or more system data bus interfaces 2, a control register 3, a command arbiter 4, a command queue and a reordering module 5, and a read flag advanced first Output module 6 and DDR2SDRAM interface 7.

[0089] The system configuration bus interface 1 uses an asynchronous design for receiving configuration bus (Config Bus) system configuration information and storing it in the control register 3, and isolating the system configuration bus clock and the DDR2 SDRAM controller clock.

[0090] The control register 3 is used to output working parameters according to the system configuration inform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More