Method for decreasing series resistors of P type substrate hetero junction with intrinsic thin layer (HIT) solar cell

A technology for solar cells and substrates, applied in circuits, photovoltaic power generation, electrical components, etc., can solve problems such as reducing battery open circuit voltage and increasing series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

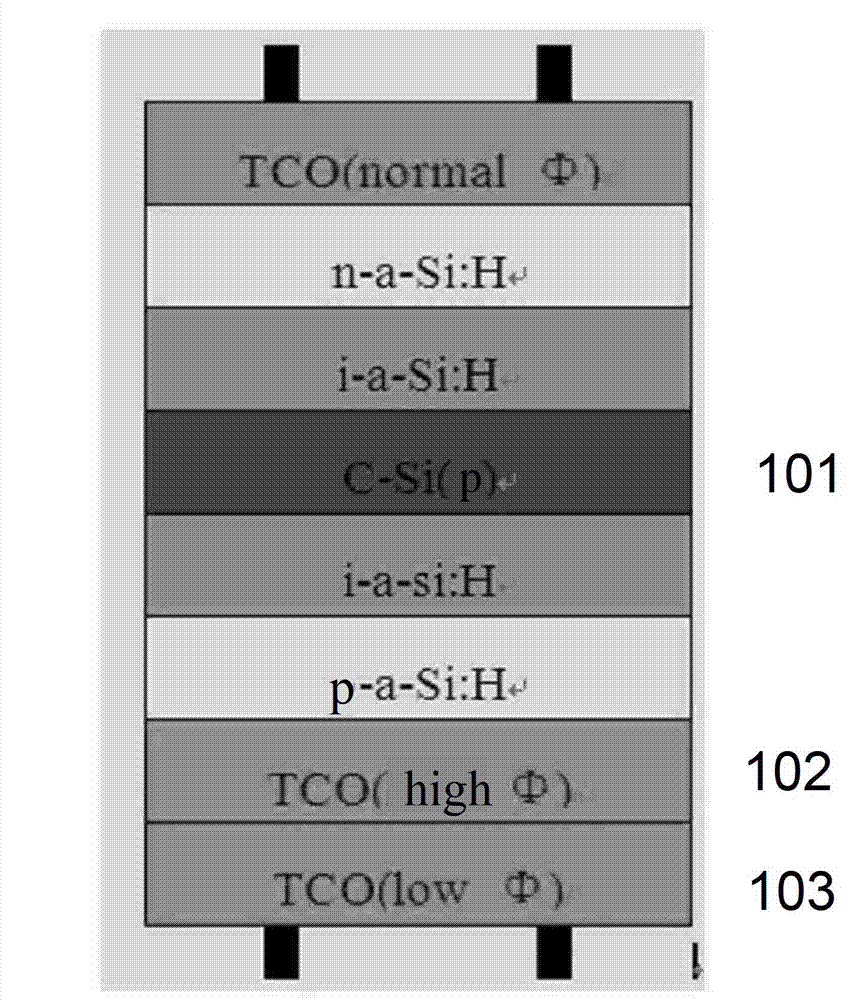

[0019] P-type substrate HIT battery:

[0020] Such as figure 1 As shown, an embodiment of the present invention uses a P-type silicon wafer to make a P-type substrate HIT cell. Compared with the existing P-type substrate HIT battery, the main difference is that the outside of the p-a-si:H layer (the side opposite to the middle P-type substrate 101) is sequentially covered with a high work function TCO layer 102 and a low work function TCO layer 103 .

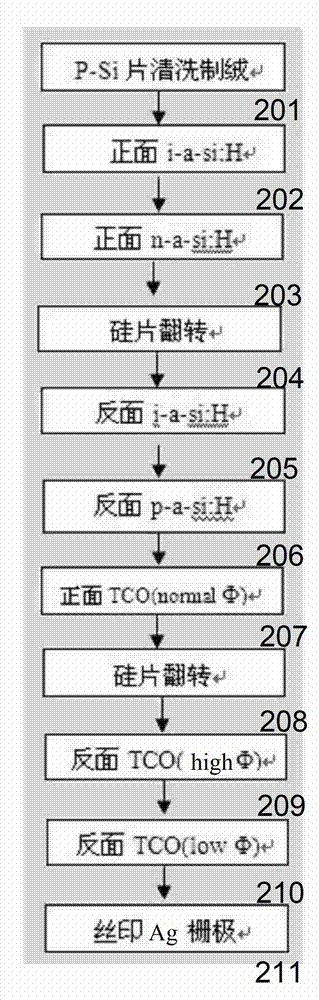

[0021] figure 1 An exemplary fabrication method for the shown P-type substrate HIT cell is described in figure 2 middle. Firstly, the p-type silicon wafer is strictly cleaned and textured (201), and then the PECVD method is used to deposit and grow i-a-si:H of about 1-10nm and n-a-si:H of about 1-10nm (202 and 203 ); then turn over the silicon wafer ( 204 ), on the other side of the silicon wafer, still use PECVD method to deposit and grow 1-10nm i-a-si:H and 10-20nm p-a-si:H ( 205 and 206 ). Then use the reactive plasma ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Work function | aaaaa | aaaaa |

| Work function | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap