Array substrate, manufacture method of array substrate and display device

An array substrate and manufacturing method technology, applied in the field of display, can solve the problems of slow development of LTPSTFT technology, difficult competition of amorphous silicon TFT products, and various production processes, so as to reduce the number of patterning processes, shorten production time, and improve product quality Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

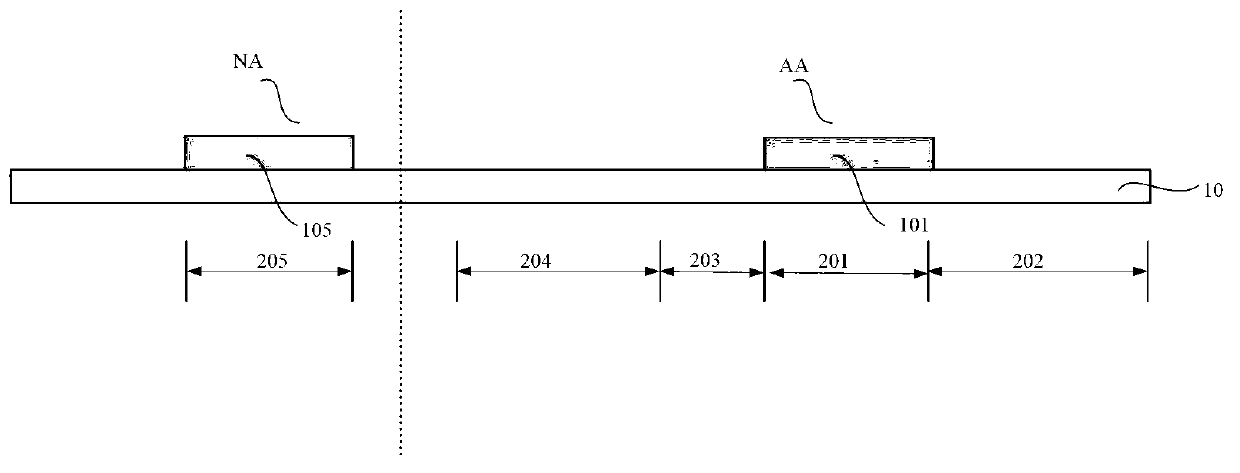

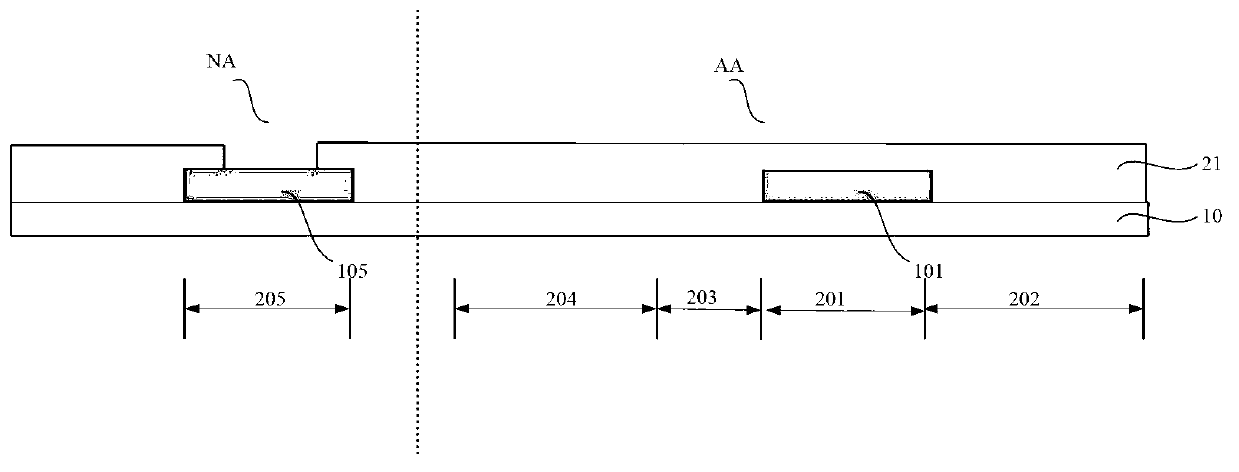

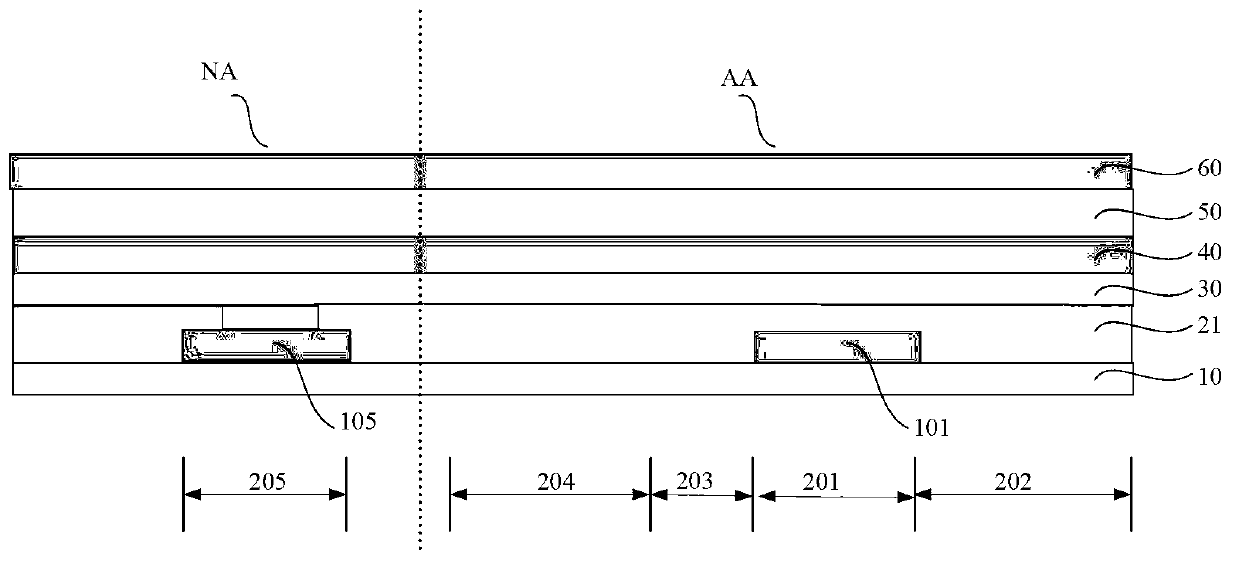

[0066] Combine below Figure 1 to Figure 9 The manufacturing method of the array substrate in the embodiment of the present invention will be described in detail.

[0067] The manufacturing method of the array substrate in the embodiment of the present invention includes forming a thin film transistor and a pixel electrode pattern on a base substrate. The thin film transistor at least includes a gate electrode pattern, an active layer pattern, a source electrode pattern and a drain electrode pattern,

[0068] Wherein, the source electrode pattern, the drain electrode pattern, the pixel electrode pattern and the active layer pattern are formed in one patterning process through a three-gray-level mask process.

[0069] The source pattern, drain pattern, pixel electrode pattern, and active layer pattern are formed in one patterning process through the three-gray-level mask process, which can reduce the number of times the mask is used, simplify the production process, and greatly reduce ...

Embodiment 2

[0113] In this embodiment, an array substrate is provided, which includes a thin film transistor and a pixel electrode pattern formed on a base substrate. The thin film transistor at least includes a gate electrode pattern, an active layer pattern, a source electrode pattern, and a drain electrode pattern. The source electrode pattern, the drain electrode pattern, the pixel electrode pattern, and the active layer pattern are formed by one patterning process.

[0114] Specifically, the array substrate includes:

[0115] Base substrate

[0116] A pattern including a gate electrode on the base substrate;

[0117] A gate insulating layer pattern located above the pattern including the gate electrode;

[0118] A pattern including an active layer located above the gate insulating layer pattern, the active layer pattern being formed of an active layer thin film formed above the gate insulating layer pattern, the active layer pattern including a source electrode Region, drain region and chann...

Embodiment 3

[0148] This embodiment provides a display device, including the array substrate in the second embodiment. Since the array substrate has the advantages of low cost and high quality, the cost of the display device can be reduced and the quality of the display device can be improved.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More