Package substrate of active chip and preparation method thereof

A technology of active chips and packaging substrates, which is applied to printed circuits connected to non-printed electrical components, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of reducing the size of the package body and packaging Large structure and other problems, to achieve the effect of integrated production, improve production efficiency and simplify the production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

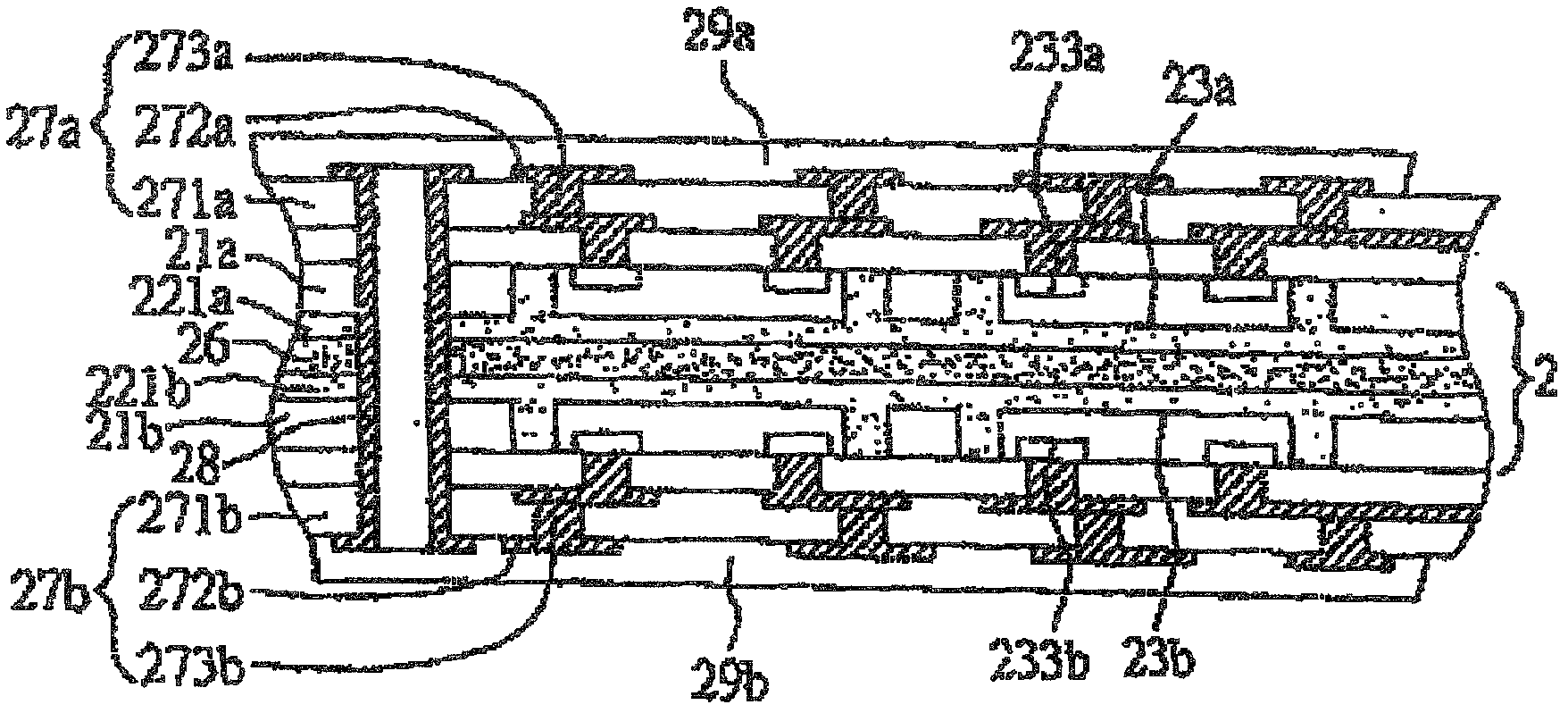

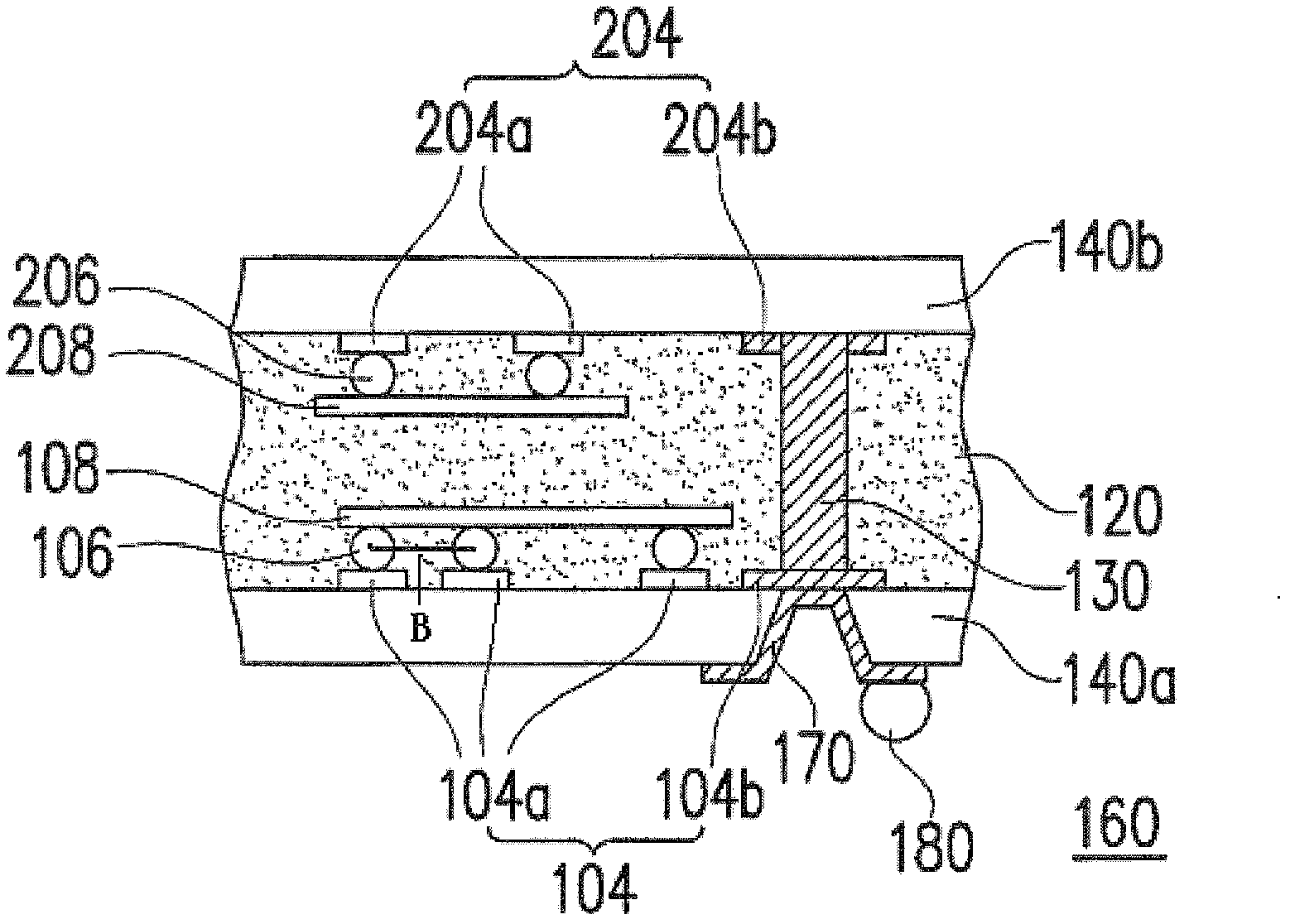

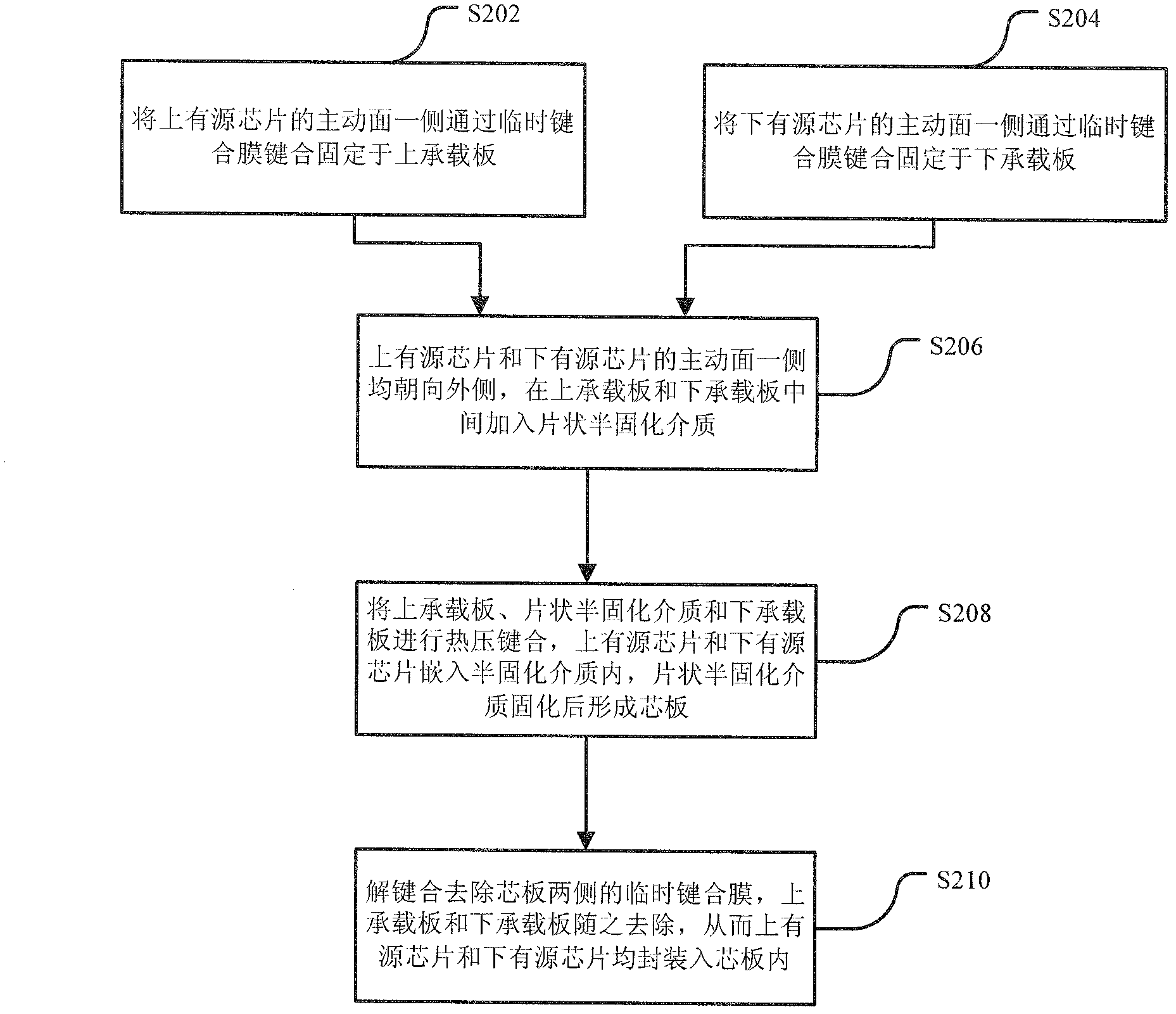

[0045]In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings. It should be noted that while examples of parameters including particular values may be provided herein, it should be understood that the parameters need not be exactly equal to the corresponding values, but rather may approximate the values within acceptable error margins or design constraints. For ease of description, at first the various components involved in the present invention are numbered:

[0046] 100-on the active chip; 101-on the metal electrode of the active chip;

[0047] 102-the first passivation layer on the active chip, with openings to expose the electrodes;

[0048] 103 - the second passivation layer on the active chip;

[0049] 104 - temporary bonding film;

[0050] 105-upper bearing plate;

[005...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More