Field programmable gate array (FPGA)-based superfast auxiliary encoder system (AES) processor and implementing method thereof

A processor, ultra-high-speed technology, applied in the field of communication, can solve problems such as large resource occupation, long delay time, complex control logic, etc., to achieve the effect of ensuring effectiveness, improving reliability, and simple storage control logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings.

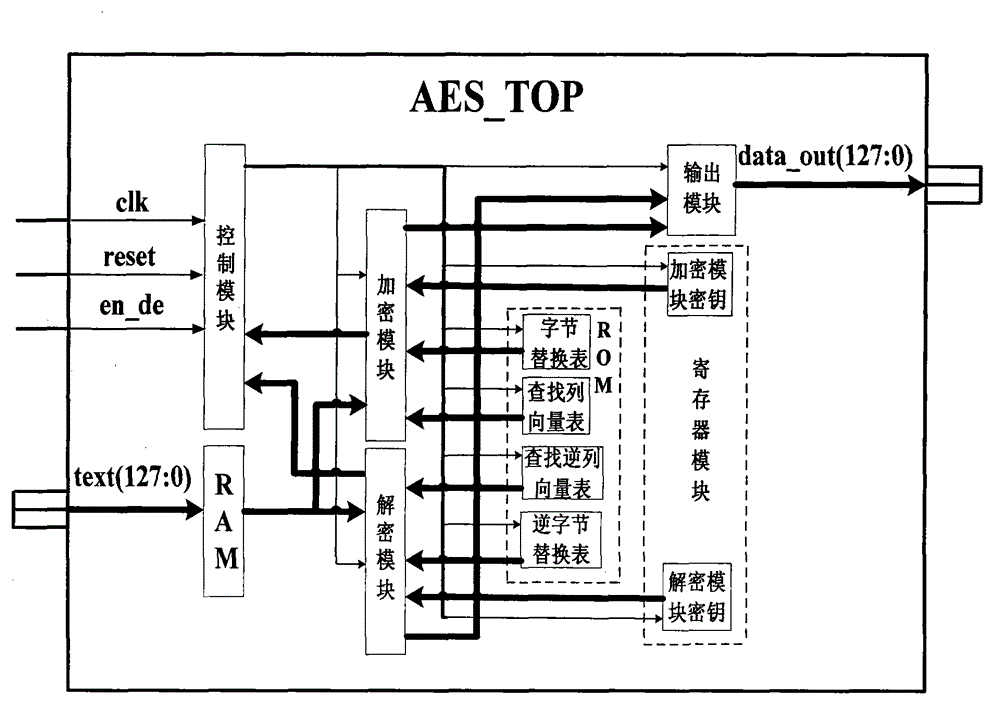

[0043] Refer to attached figure 1 The overall structure of the processor of the present invention is further described.

[0044] The processor of the present invention includes an interface storage area buffer module, a control module, an AES encryption and decryption module, a read-only memory lookup table module, a register module, and an output module; the interface storage area buffer module and the AES encryption and decryption module are connected through a data bus and a control bus ; The read-only memory look-up table module, the register module, the control module and the output module are connected through the data bus and the control bus.

[0045] The interface storage area buffer module is used for temporarily storing the data on the input data bus. The interface storage area buffer module includes four random access memory RAMs arranged in the front buff...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com