Through-silicon via (TSV) testing structure and TSV testing method

A test structure and test method technology, which is applied in the direction of single semiconductor device test, electromagnetic measurement device, electric/magnetic area measurement, etc., can solve the problem of not testing the interconnection structure, etc., and achieve the effect of convenient and fast detection method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

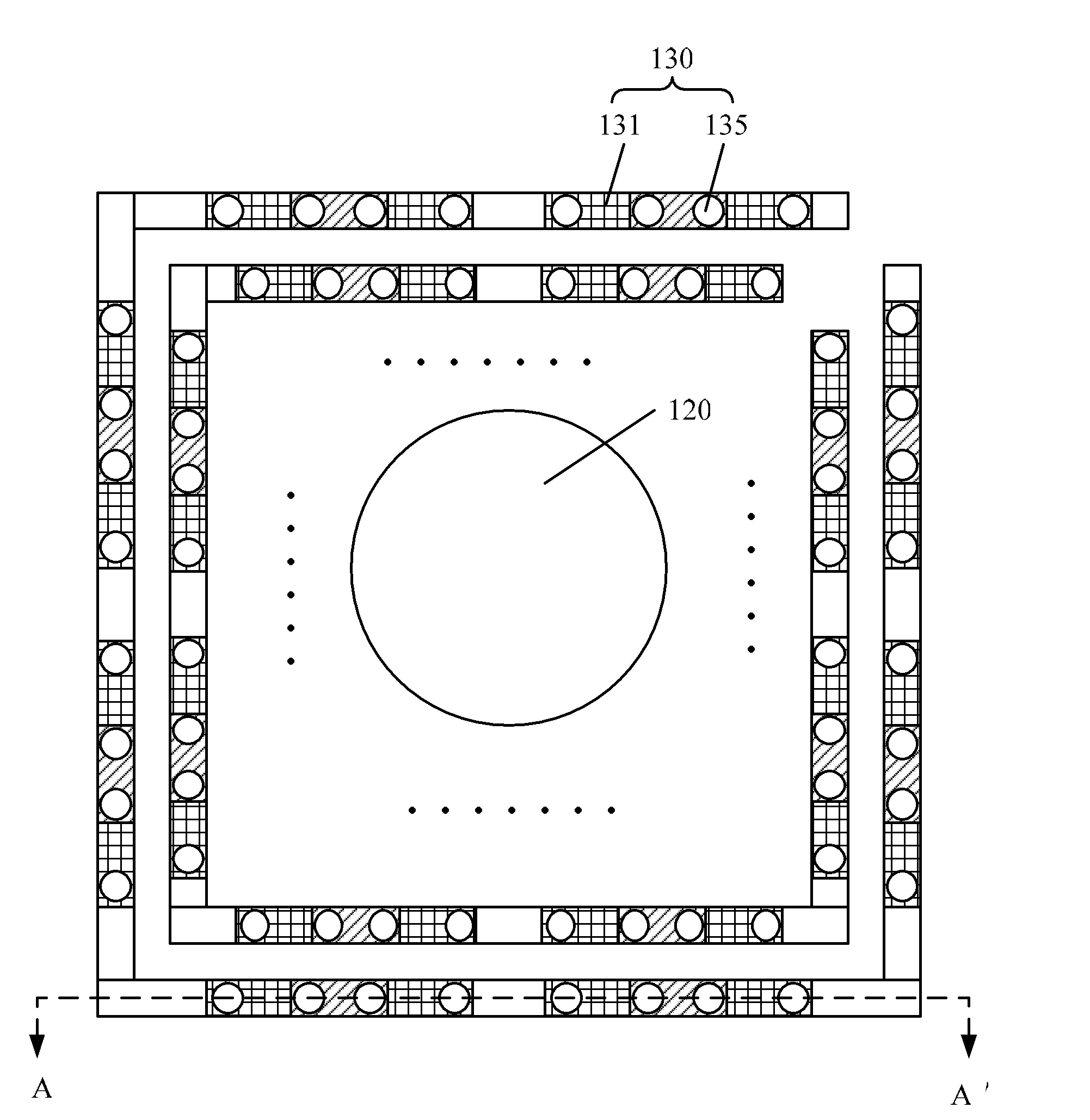

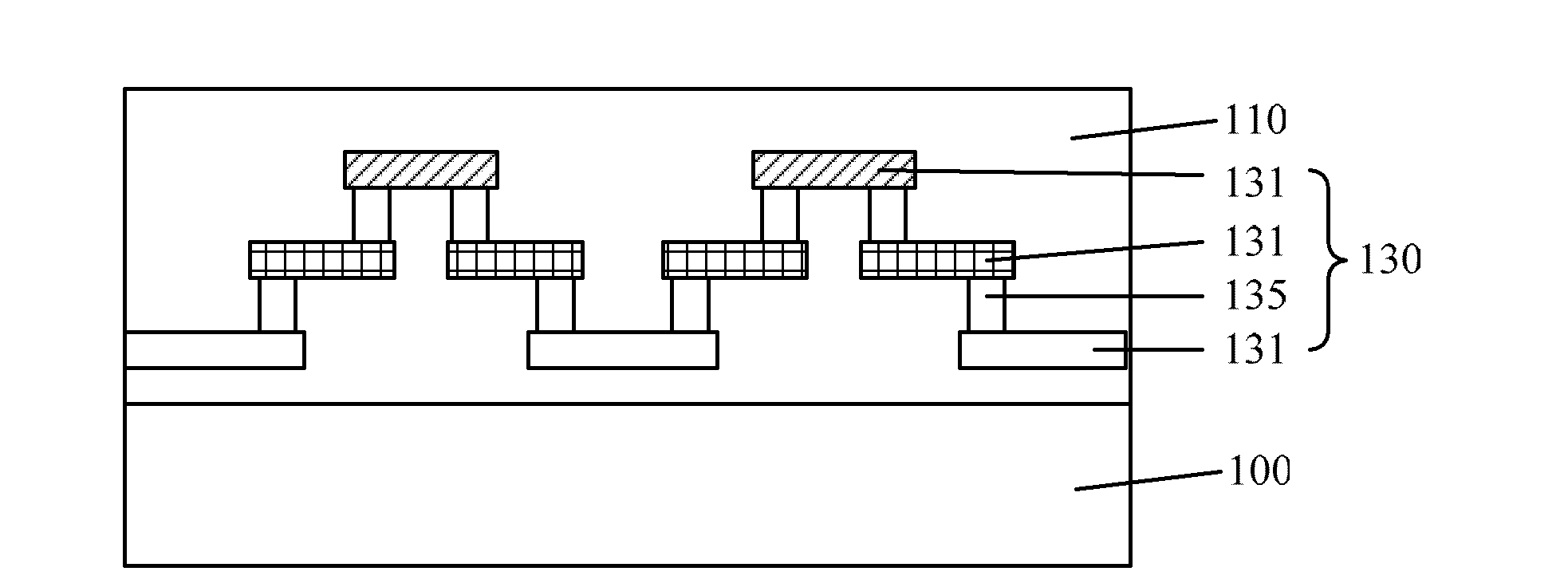

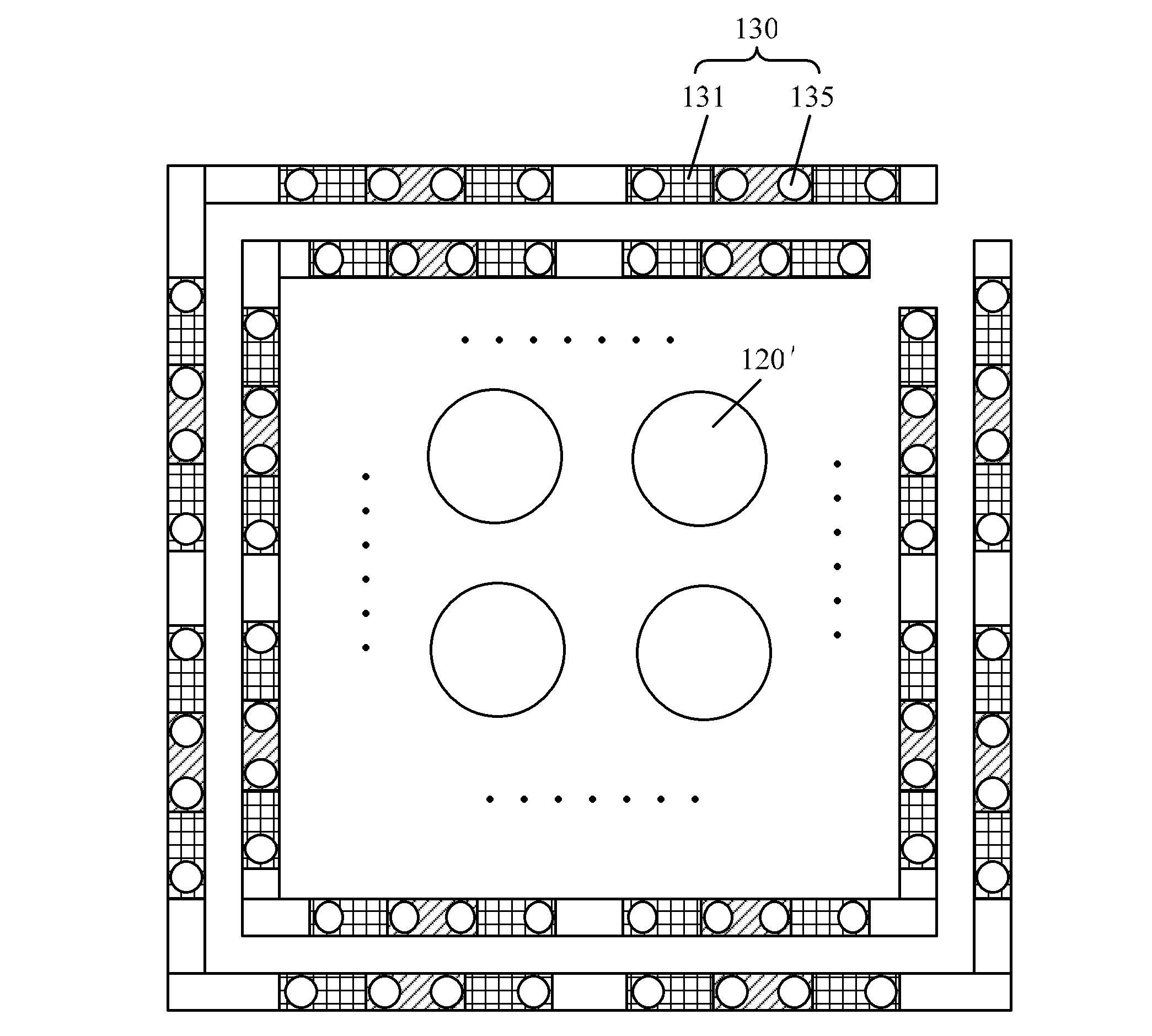

[0034] In the prior art, in order to realize three-dimensional stacking of chips, through-silicon vias penetrate the entire semiconductor substrate to realize electrical connection between the upper and lower chips. Wherein, the TSV is filled with copper. However, when the temperature of the semiconductor substrate changes, due to the thermal expansion coefficient mismatch between the copper and the semiconductor substrate, it is easy to cause the TSV to generate tensile or compressive stress on the surrounding semiconductor substrate and interlayer dielectric layer, The tensile or compressive stress changes the lattice of the interlayer dielectric layer and the metal interconnection layer finally formed around the TSV, thereby changing the electrical properties of the interconnection structure. Moreover, as more and more integrated circuits use low-K dielectric materials as the material of the interlayer dielectric layer, due to the low mechanical strength of the low-K dielec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More