Field programmable gate array (FPGA) device for diagnosing and predicting artificial circuit faults

A technology for simulating circuit faults and simulating circuits, which is applied in the direction of analog circuit testing, electronic circuit testing, etc., can solve the problems of lack of verification platform for analog circuit fault diagnosis and prediction algorithms, data processing lag, and staying in the simulation stage, etc., to achieve simulation Circuit fault diagnosis and prediction Real-time and remote monitoring, the effect of high circuit integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described below in conjunction with drawings and embodiments.

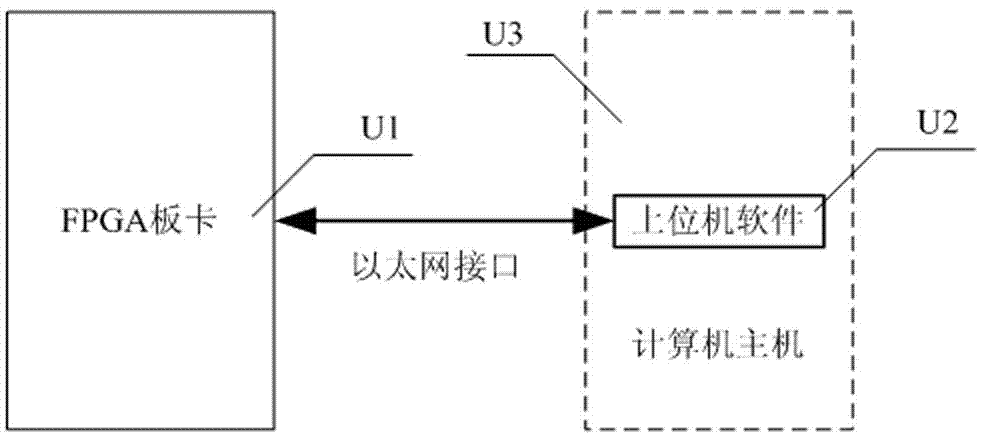

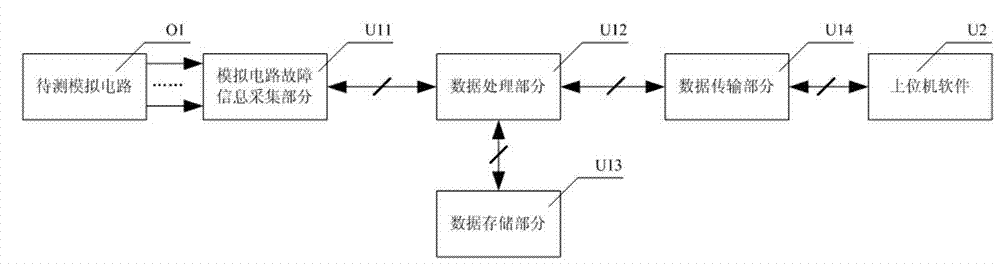

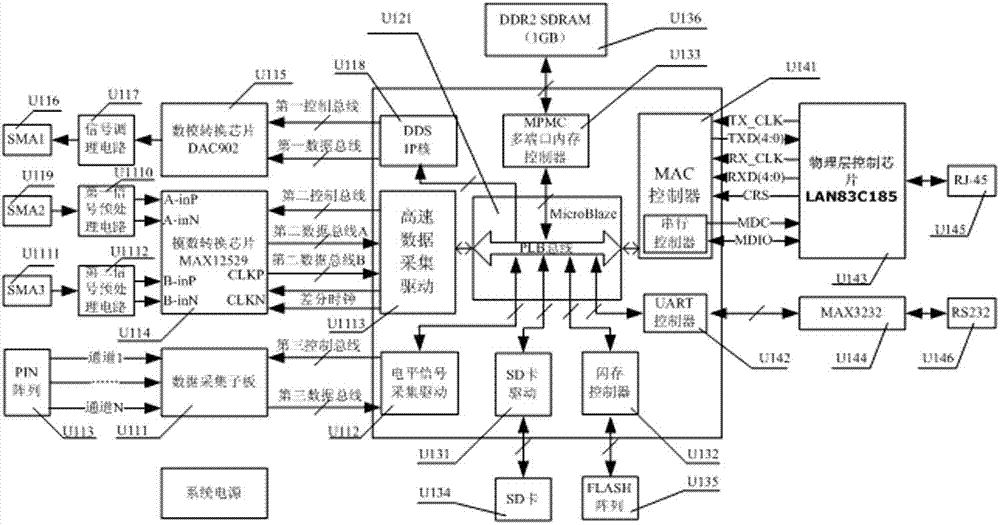

[0051] refer to figure 1 , the FPGA device used for analog circuit fault diagnosis and prediction of the present invention includes an FPGA board U1, the FPGA board U1 is connected to the computer host U3 by means of Ethernet communication, and the host computer software U2 runs in the computer host U3.

[0052] The FPGA board U1 is used to complete the collection, buffering, preprocessing, and backup of the accessible node voltage information and network spectrum characteristic data of the analog circuit to be tested, and package and transmit the original signal and analog circuit fault information to the host computer software U2;

[0053] Described upper computer software comprises ethernet driver program and interface software;

[0054] The host computer software U2 is used to receive the data frame sent by the FPGA board, provide interface software for analog circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More