Blind buried orifice plate laminating method and blind buried orifice plate manufactured with blind buried orifice plate laminating method

A blind and buried via board and substrate technology, which is used in the manufacture of multilayer circuits, the structural connection of printed circuits, and the formation of electrical connections of printed components. Accuracy and other issues, to achieve the effect of thermal stress balance, warpage improvement, and accuracy improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The following will clearly and completely describe the technical solutions in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

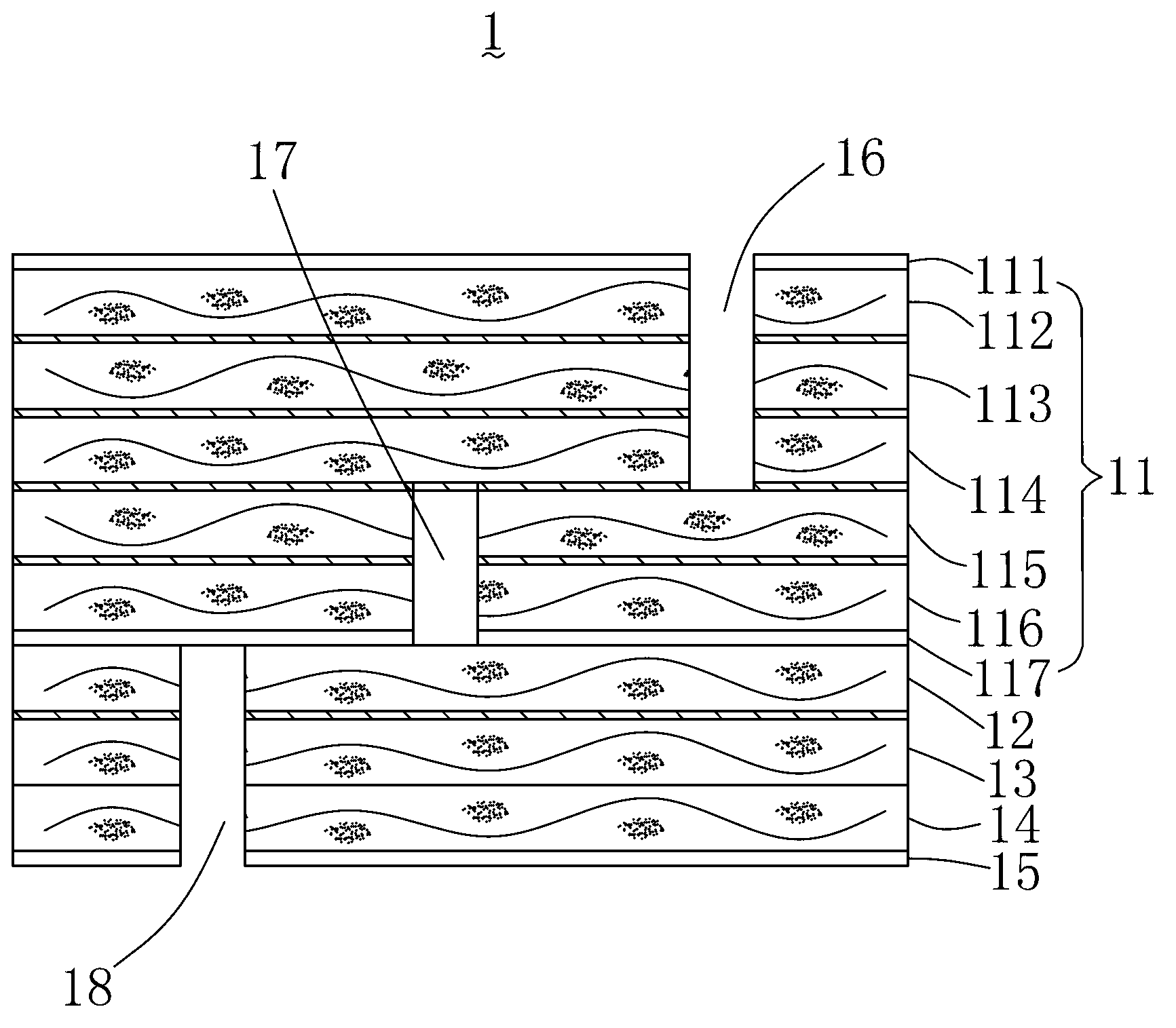

[0019] Please refer to figure 1 , is a side cross-sectional view of a preferred embodiment of the blind buried plate of the present invention. The blind and buried via plate 1 includes a first substrate 11 , a second substrate 13 and a first circuit layer 15 which are superimposed on each other. The second substrate 13 is sandwiched between the first substrate 11 and the first circuit layer 15 . The first substrate 11 and the second substrate 13 are separated by a first insulating layer 12 . The second substrate 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More