Reusable logical gate of mixed structure of MOS transistor and single-electron transistor

A single-electron transistor, multiplexing logic technology, applied in the direction of logic circuits with logic functions, etc., can solve the problem of difficult to meet circuit power consumption, integration, reliability, difficult MOS tubes to reduce the use of MOS tubes, and poor logic circuit programmability. and other problems, to achieve the effect of simple structure, reduced number of devices, and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

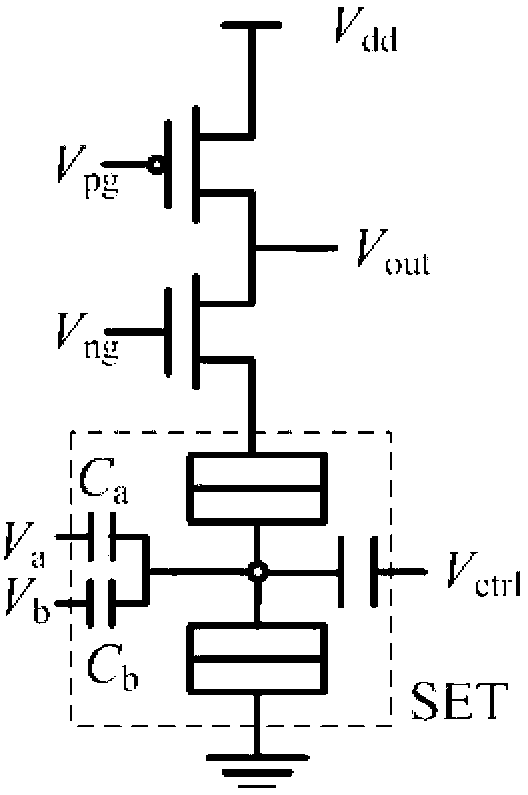

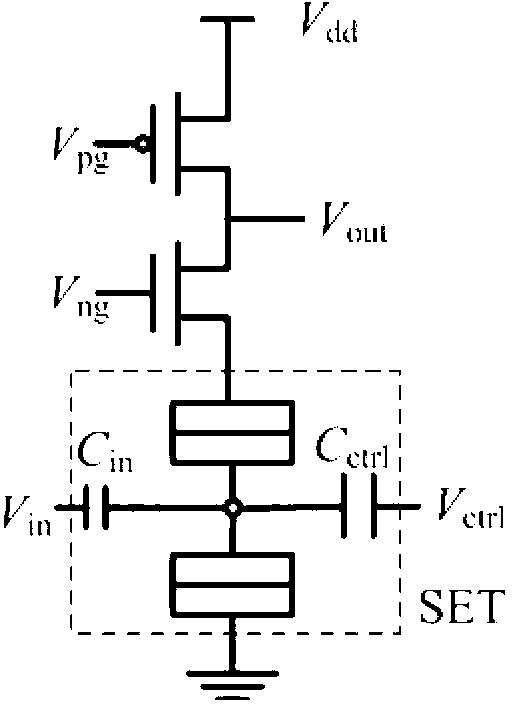

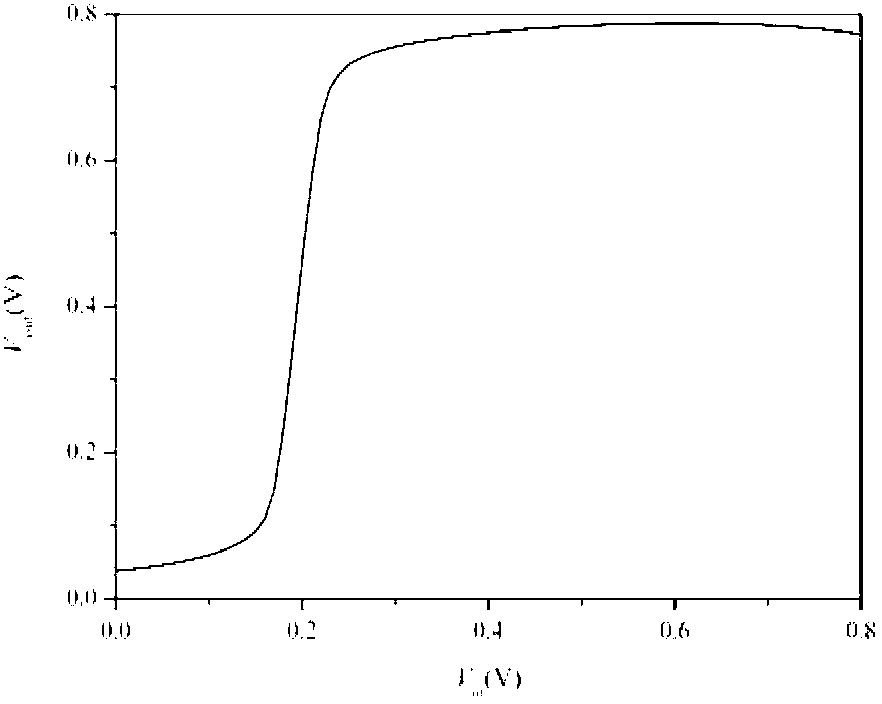

[0027] The invention designs a reusable logic gate based on the novel nanometer electronic device. This logic gate can implement all two-input logic. The novel nanoelectronic device adopted in the present invention is a single electron transistor (Single electron transistor, SET). As a typical representative of a new generation of nanoelectronic devices, SET has extremely low power consumption and ultra-small device size, and has obvious advantages over traditional microelectronic devices in terms of power consumption and working speed. Ideal device for low power consumption, high density VLSI. SET has unique Coulomb blocking and Coulomb oscillation effects, and is well compatible with MOS devices. The SET / MOS hybrid structure has the superior performance of both SET and MOS transistors, showing extremely low power consumption, ultra-small device siz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More