Method for exposing through silicon via

A technology of through-silicon vias and dielectric layers, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of shallow-dish effect, inability to expose part of the sidewalls of through-silicon vias, and disadvantages. The effect of reliable interconnection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

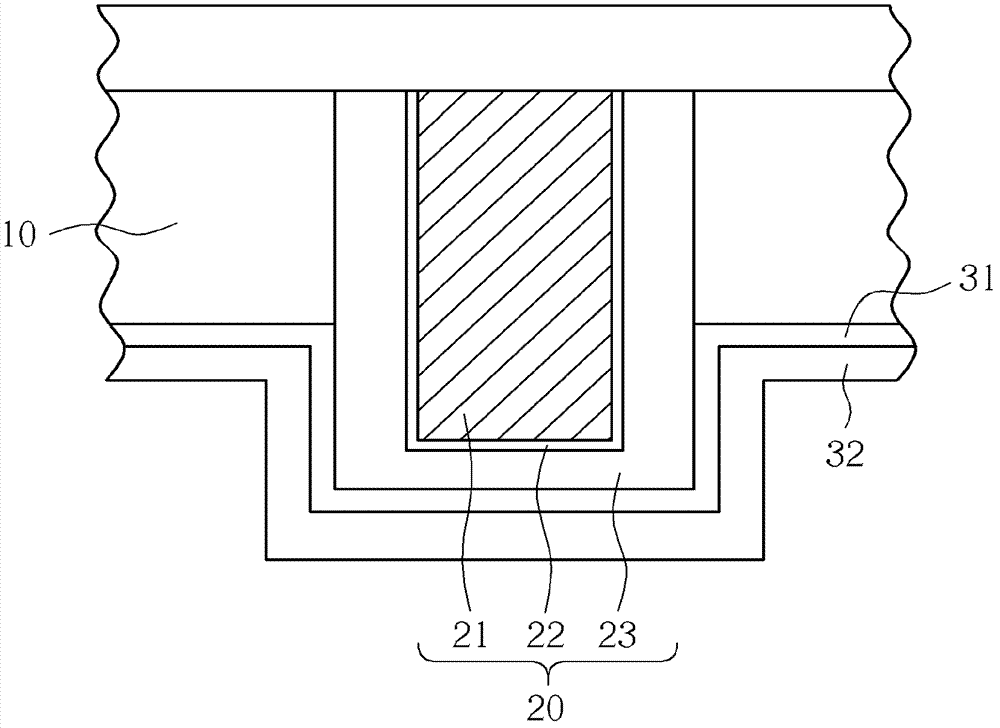

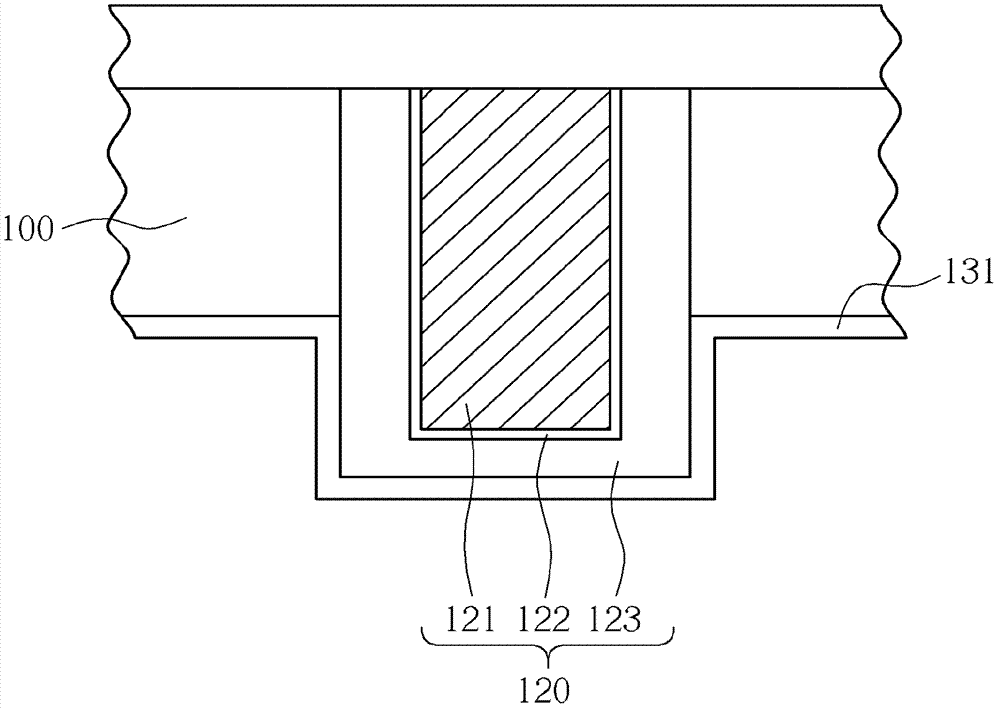

[0021] Figure 3 to Figure 7 A preferred embodiment of the present invention is illustrated. Such as image 3 As shown, firstly a TSV 120 is formed in a semiconductor substrate 100 or a silicon wafer, including a copper metal layer 121 , a barrier layer 122 and an insulating layer 123 . One end of the TSV 120 will slightly protrude from the bottom surface of the semiconductor substrate 10 or silicon wafer, such as image 3 As shown, then, a dielectric layer 131 , such as a silicon nitride layer, is covered on the bottom surface of the semiconductor substrate 10 and the TSV 120 .

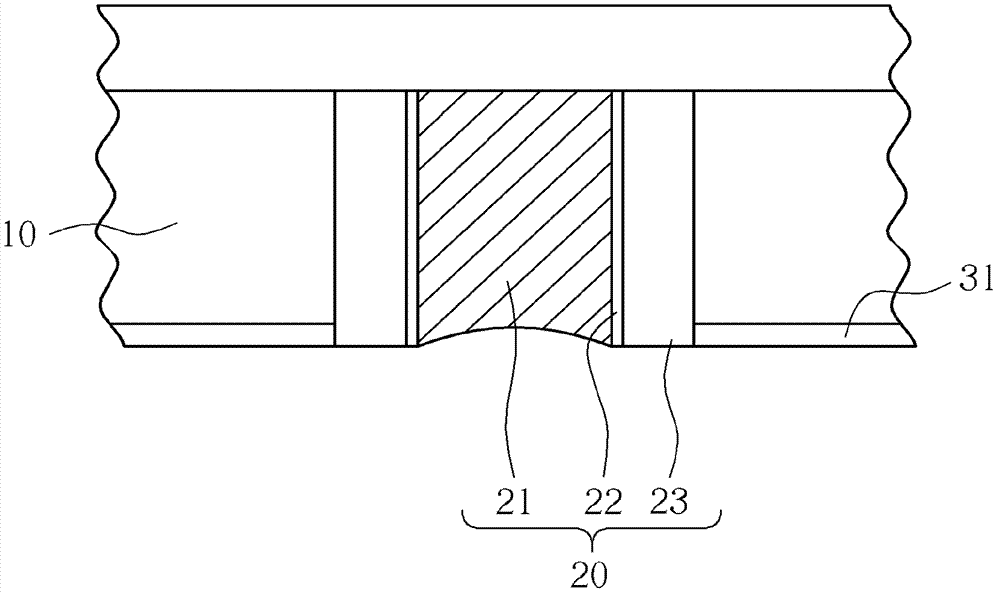

[0022] Such as Figure 4 As shown, then, a sacrificial layer 140 such as a photoresist layer is formed on the silicon nitride layer 131 . Of course, the sacrificial layer 140 can also be made of other materials, but it must be a material capable of resisting etching. Such as Figure 5 As shown, a crystal back grinding or chemical mechanical polishing (CMP) process is performed to remove part of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More