Data packet processing board and processing method

A processing method and data packet technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve problems such as uneven load, reduce system computing density, increase NP access memory pressure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

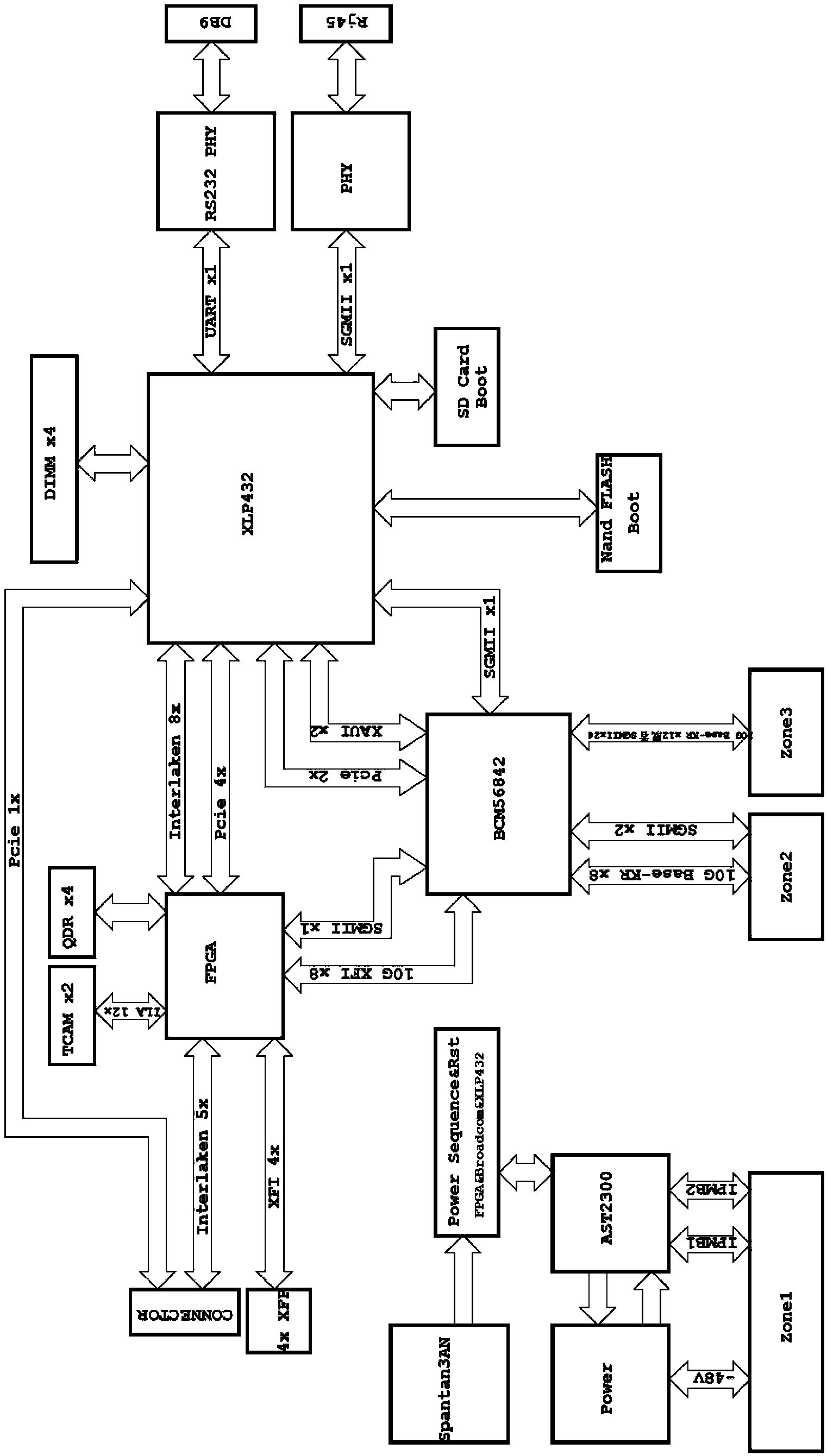

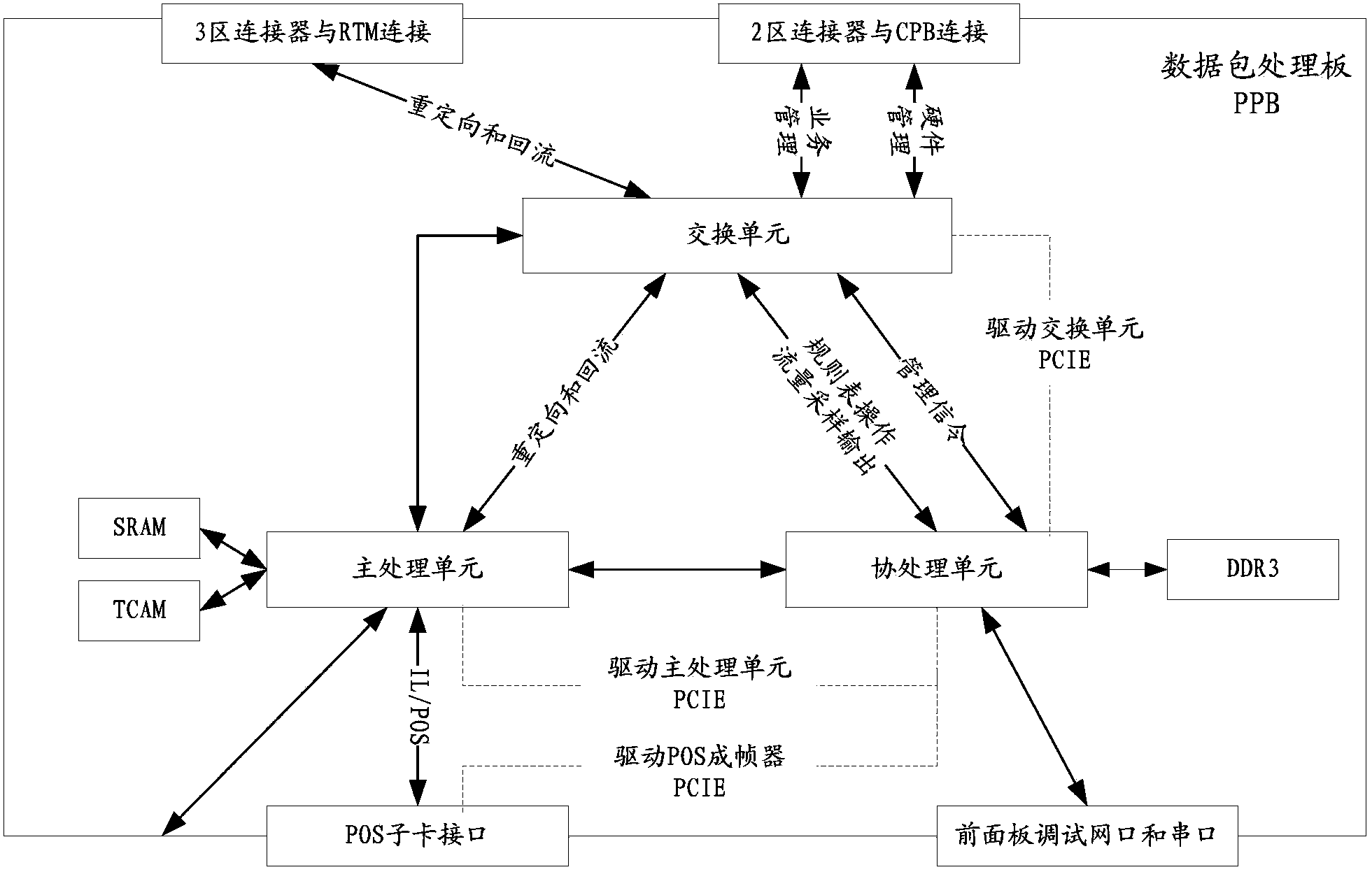

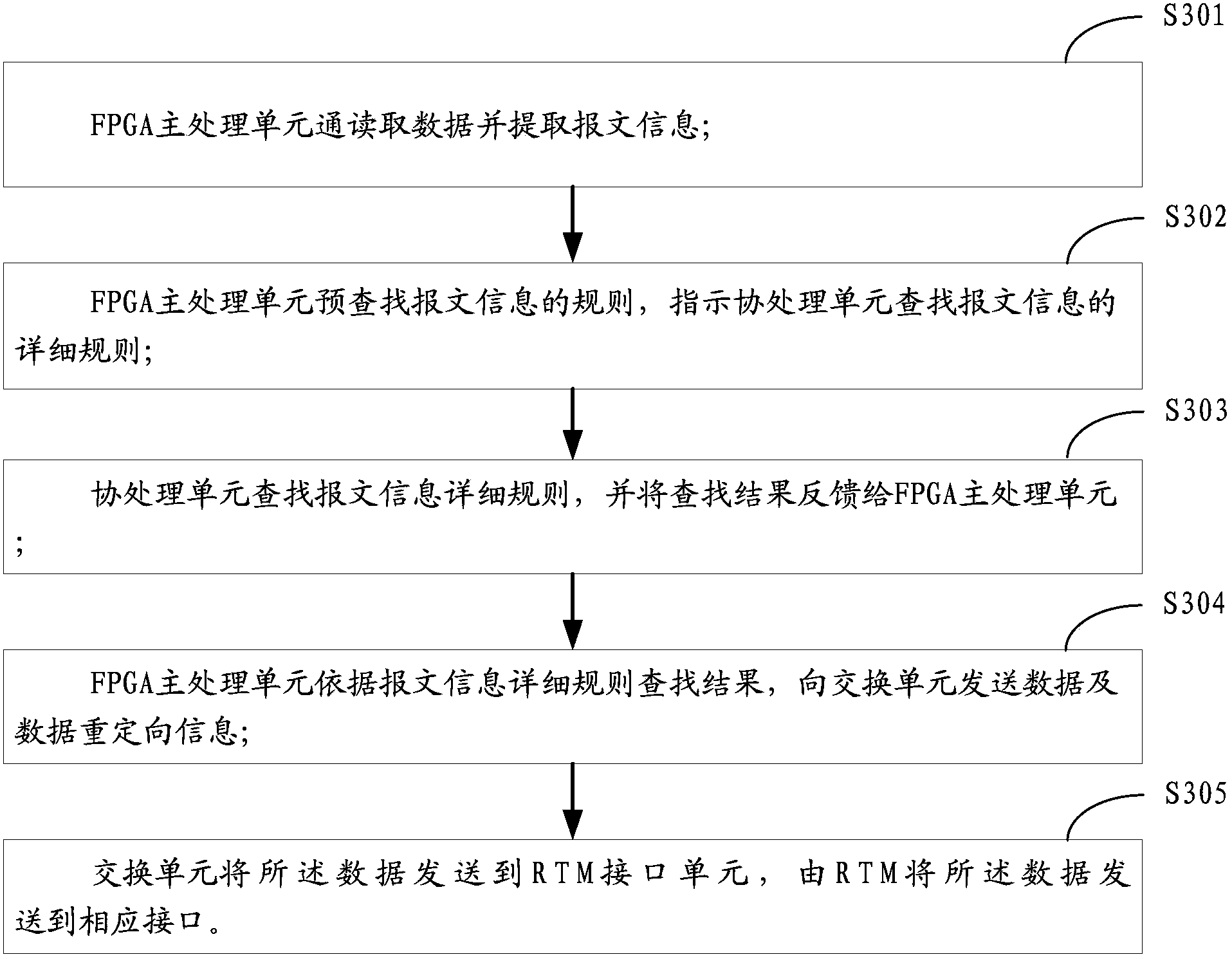

[0021] Such as figure 1 As shown, the present invention provides a data packet processing board, including: FPGA (Field-Programmable Gate Array) main processing unit, co-processing unit, switching unit, POS (Package over SDH, using SDH backbone) Intermediate protocol layer for network transmission of IP packets) daughter card interface unit, CPB (Control Processing Board, control processing board) interface unit, RTM (Rear Transition Module) interface unit, QDR (Quad Data Rate, 4 times the rate) SRAM), TCAM (Ternary Content Addressable Memory, tri-state content addressable memory) and DDR3, where the FPGA main processing unit is connected to the POS daughter card interface unit, and is connected to the co-processing unit through the Interlaken bus, and through the GE or 10GE bus Connected to the switching unit, the FPGA main processing unit is used to receive data, extract message information, pre-search message information, instruct the co-processing unit to search for detailed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More