Network-on-chip-based optimization method for DRAM communication

An optimization method and network-on-chip technology, applied in the fields of instruments, electrical digital data processing, computers, etc., can solve problems such as performance degradation, VC number reduction, cache resource utilization reduction, etc., to achieve overall performance increase, reduce delay, improve The effect of utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described in detail below in conjunction with the accompanying drawings.

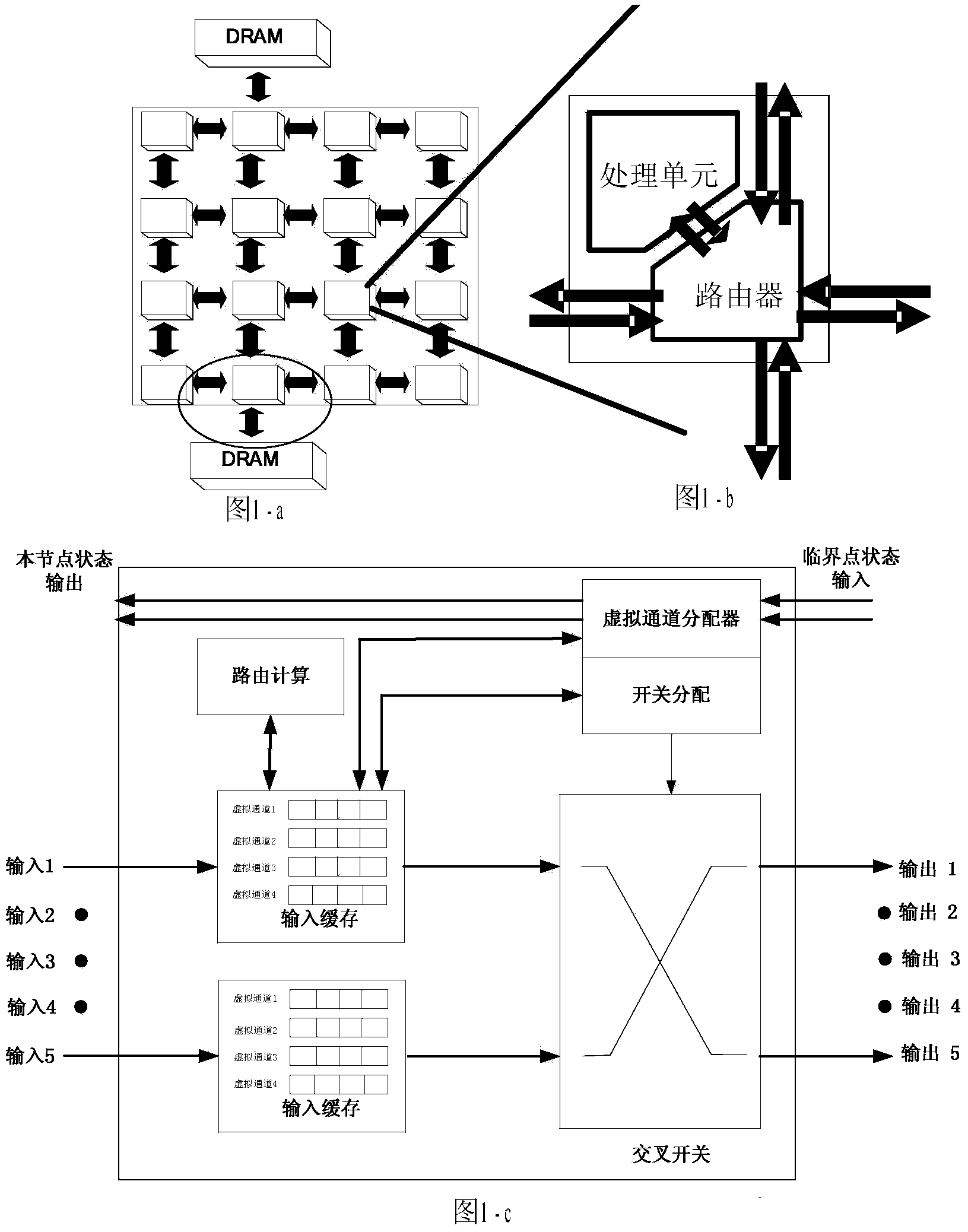

[0020] figure 1 -a is a system schematic diagram of a standard two-dimensional grid topology based on an on-chip interconnection network communication system, including a processing unit, a communication link, and a storage controller. Each square node represents a processing unit, such as CPU, DSP, etc. The double arrows indicate the communication links of the network. The oval area in the figure emphasizes the interface between the on-chip network and DRAM, which connects the on-chip network and DRAM. figure 1 -b is figure 1 - the architecture of a processing unit in a, as shown in the figure, each processing unit includes a processor and a corresponding routing unit.

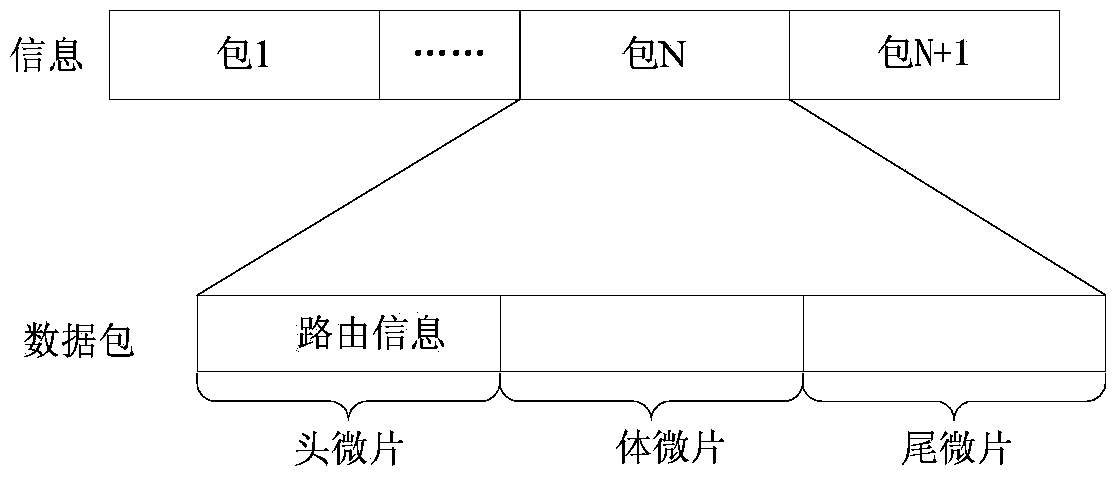

[0021] figure 1 -c is a structure diagram of a standard NoC five-stage pipeline router in the prior art, specifically including: write input buffer, routing path calculation, virtual ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More