Orthogonal base-based cdma network-on-chip architecture and its implementation

An on-chip network and implementation method technology, which is applied in the fields of instruments, electrical digital data processing, computers, etc., to ensure correct reception, simple structure, and save chip area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

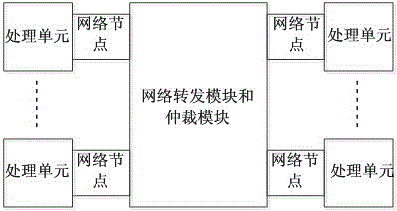

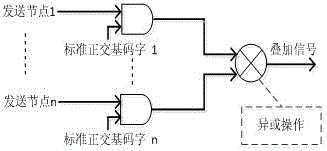

[0039] In order to solve the problems of low code word utilization and waste of resources in the traditional Walsh code encoding method, such as Figure 1~4 As shown, the present invention designs a CDMA network-on-chip architecture based on the standard orthogonal basis, which effectively increases the adaptability and flexibility in practical applications by using the standard orthogonal basis encoding method, and can save chip area and power consumption, which is beneficial to realize the cost control of the code division multiplexing network on chip.

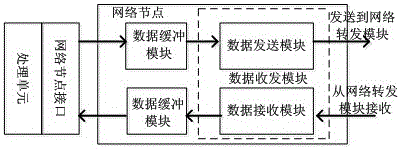

[0040] Such as figure 1 , figure 2 As shown, the present invention includes a plurality of processing units, a network node interface arranged on the processing unit, a data buffer module bidirectionally connected to the network node interface, a data transceiving module bidirectionally connected to the data buffer module, a bidirectionally connected data transceiving module, An integrated network forwarding module and ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More