Ultralow-power-consumption mixed type content addressable memory

An addressable memory, ultra-low power consumption technology, applied in the storage field, can solve the problems of high power consumption, word structure matching line ML output error results, inverter F can not be flipped, etc., to achieve ultra-low power consumption CAM Design, improve the pre-charge ability, eliminate the effect of level jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

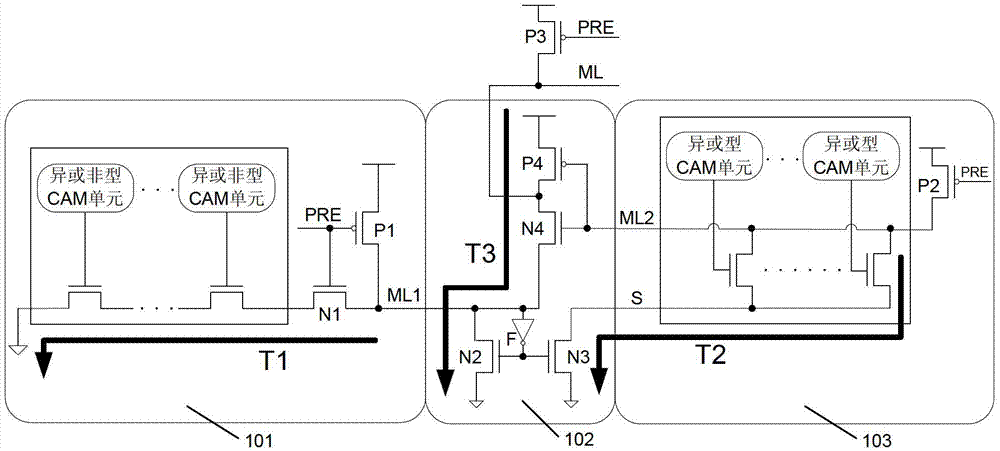

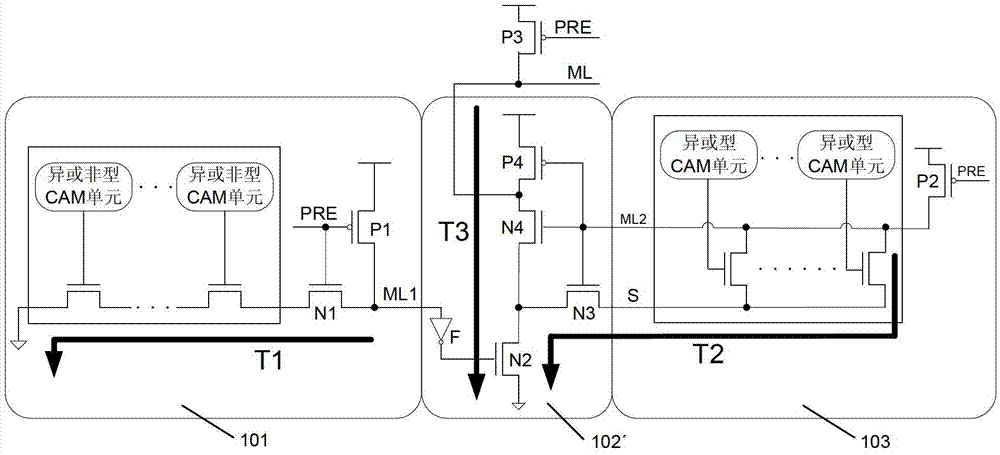

[0034] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0035] The ultra-low power consumption hybrid content addressable memory provided by the embodiments of the present invention will be described in detail below.

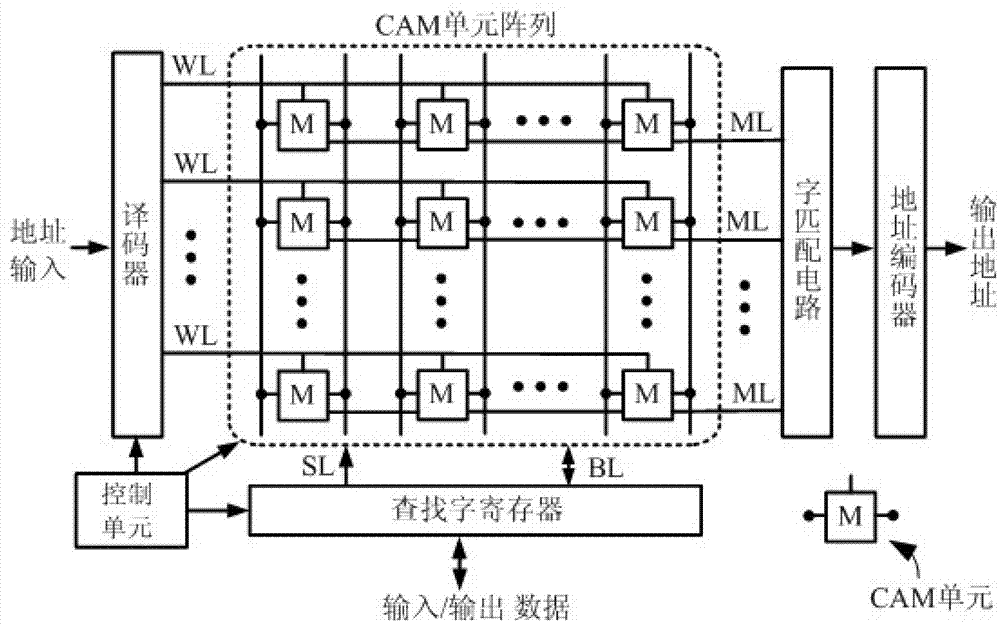

[0036] A kind of ultra-low power consumption hybrid content addressable memory, its concrete structure comprises control unit, CAM cell array and word matching circuit, can also comprise decoder, lookup word register and address coder; This CAM cell array comprises at least A hybrid CAM w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More