NoC (network on chip) resource network interface of ARM processing unit and drive method of NoC resource network interface

A technology of ARM processor and network interface, which is applied in the field of NoC resource network interface of ARM processor and its driving field, can solve the problems that have not been seen in the report of NoC resource network interface, and achieve enhanced expansion ability and network communication ability, and realize data The effect of strong communication and task ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

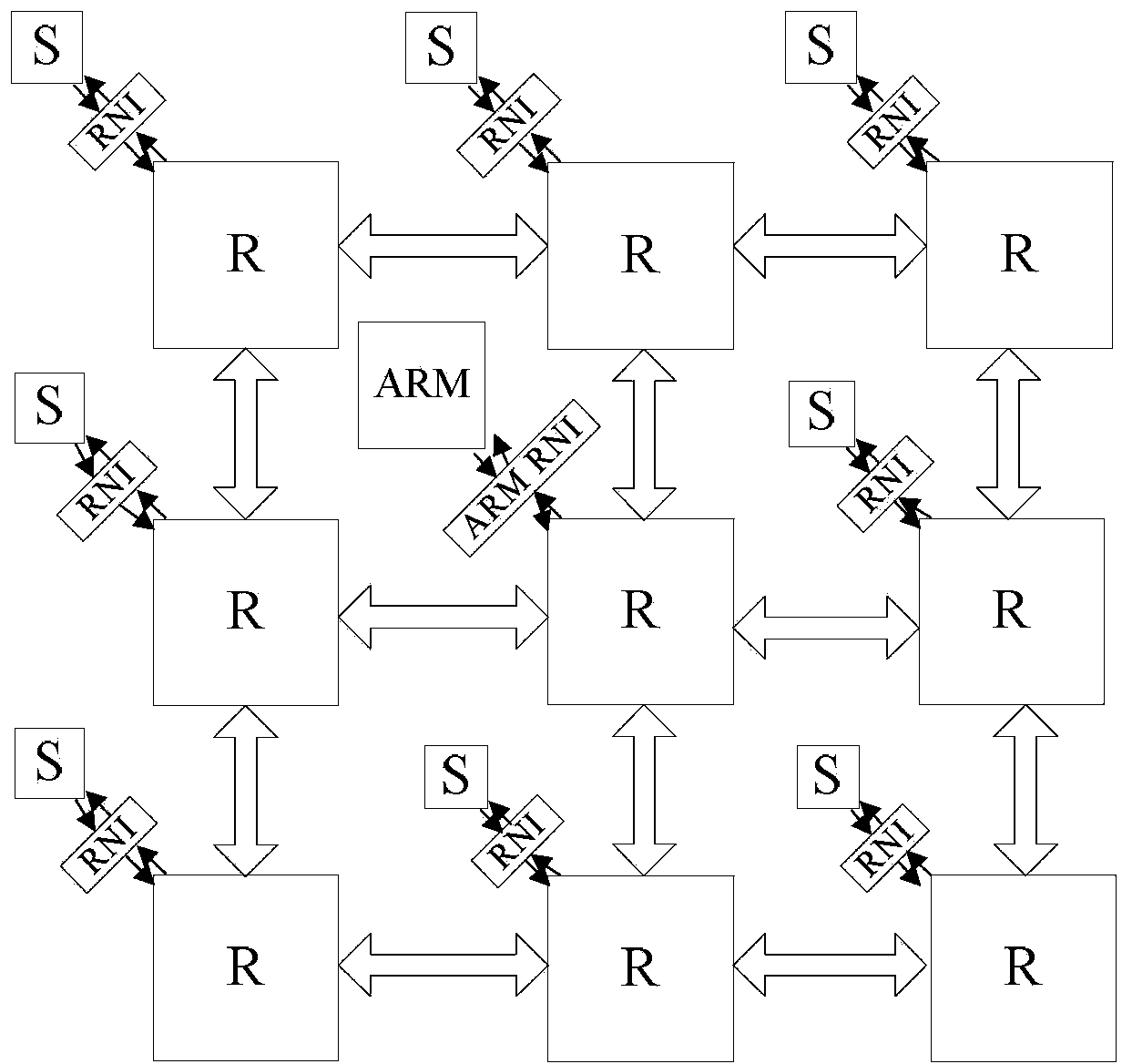

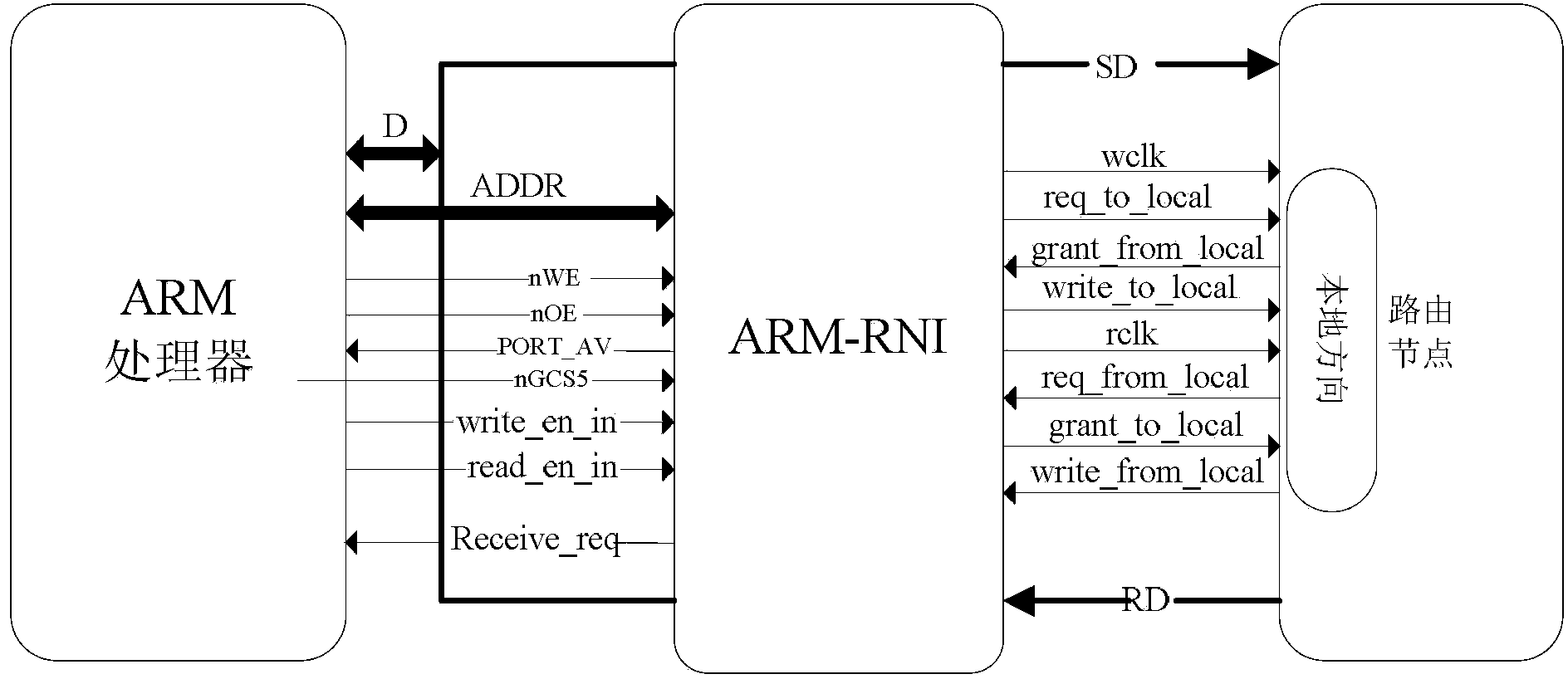

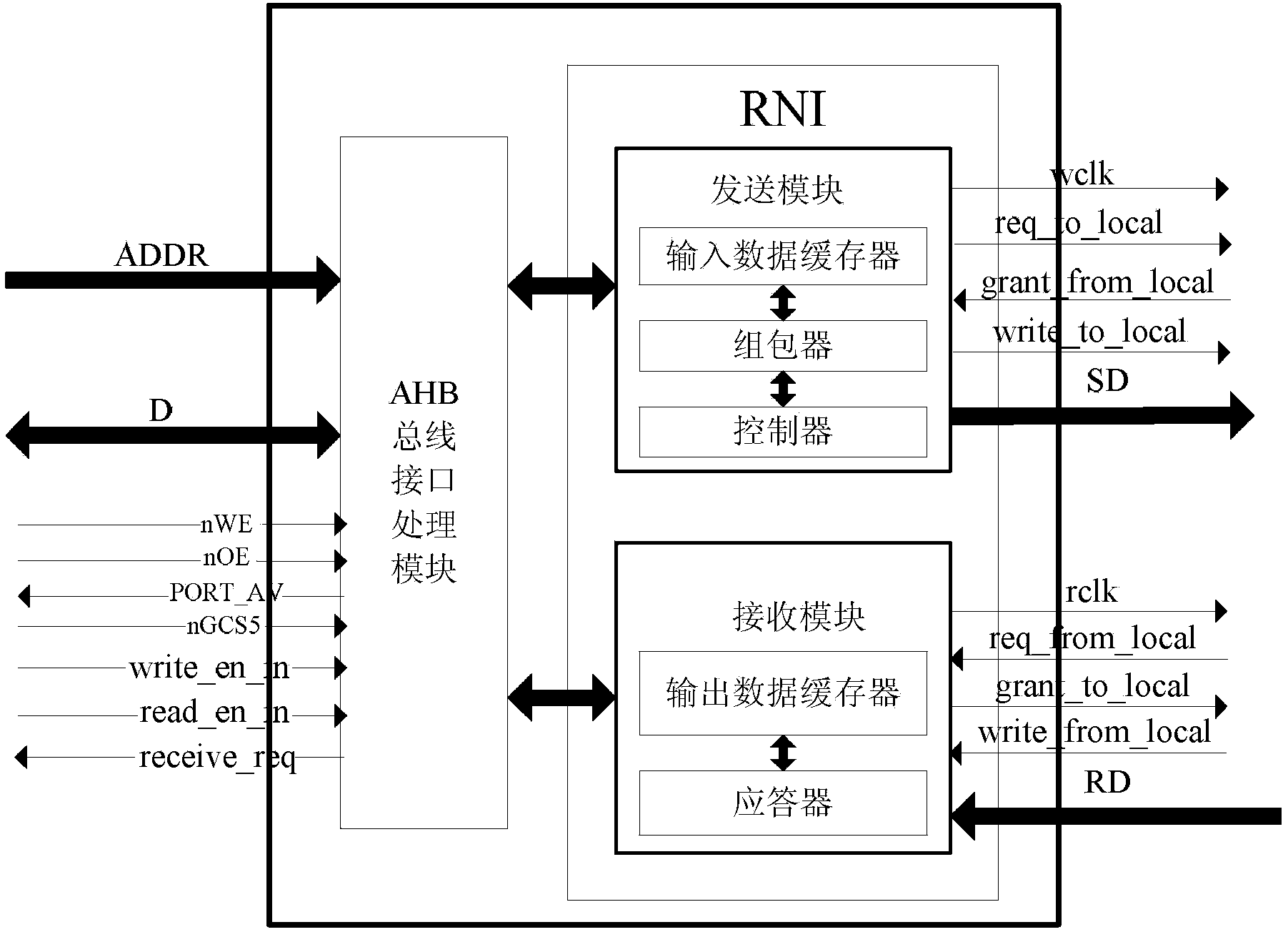

[0025] The network-on-chip NoC in the NoC resource network interface embodiment of the ARM processor is based on the FPGA chip, and its FPGA-based network-on-chip communication architecture model diagram is as follows figure 1As shown, several routing nodes R in the system are connected to each other, and the system structure is a regular 3×3 2-dimensional grid (2D-Mesh) topology structure. Routing nodes R in the NoC use wormhole data switches based on virtual channel technology Control, implemented by a deadlock-free deterministic XY-dimensional routing algorithm. In the figure, S represents a resource node of a general IP core, and RNI represents a general resource network interface (Resource Network Interface). The resource node S is connected to the routing node R of the NoC through the resource network interface RNI. ARM represents an ARM processor serving as a resource node, and ARM-RNI represents a NoC resource network interface of the ARM processor in this embodiment. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More