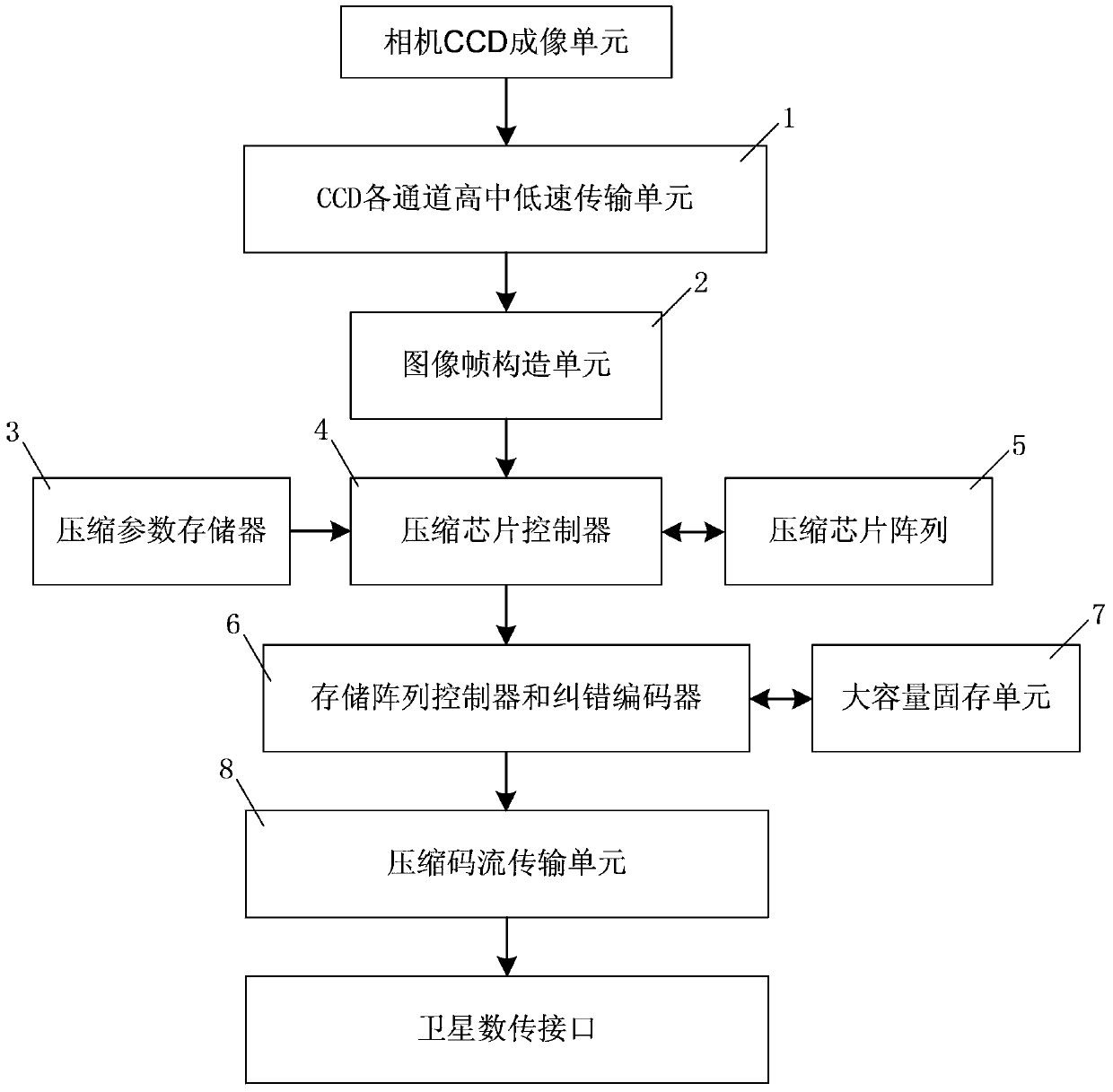

Device for real-time transmission, compression and storage of images of space TDICCD (Time Delay and Integration Charge Coupled Device) camera

A real-time transmission and storage device technology, applied in the direction of image communication, TV, color TV components, etc., can solve the problems of large resource occupation, single event flipping of image memory, complexity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Invention idea of the present invention is:

[0026] According to the possible output of low-speed, medium-speed and high-speed image data by the CCD imaging unit, the corresponding transmission system is designed, and the ECC error correction coding strategy is adopted during transmission to improve the transmission reliability. The image real-time compression unit adopts the special compression chip ADV212, according to the working characteristics of ADV212 and multi-channel CCD image output characteristics, adopts Custom working mode and frame structure strategy to realize single-chip ADV212 processing multi-channel CCD image data. The compressed code stream is stored in a large-capacity NAND flash memory. In order to prevent the phenomenon of single event flipping in the memory, this paper uses the RS error correction algorithm. Finally, the compressed code stream adopts the G-level transmission scheme, which greatly reduces the transmission channel. The whole de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com