Layering system for achieving caching consistency protocol and method thereof

A high-speed cache and coherence technology, applied in the field of integrated circuits, can solve the problems of small number of cores, high bus bandwidth requirements, low maintenance efficiency, etc., and achieve the effects of good real-time performance, improved maintenance efficiency, and reduced use frequency and occupied time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described below in conjunction with the accompanying drawings.

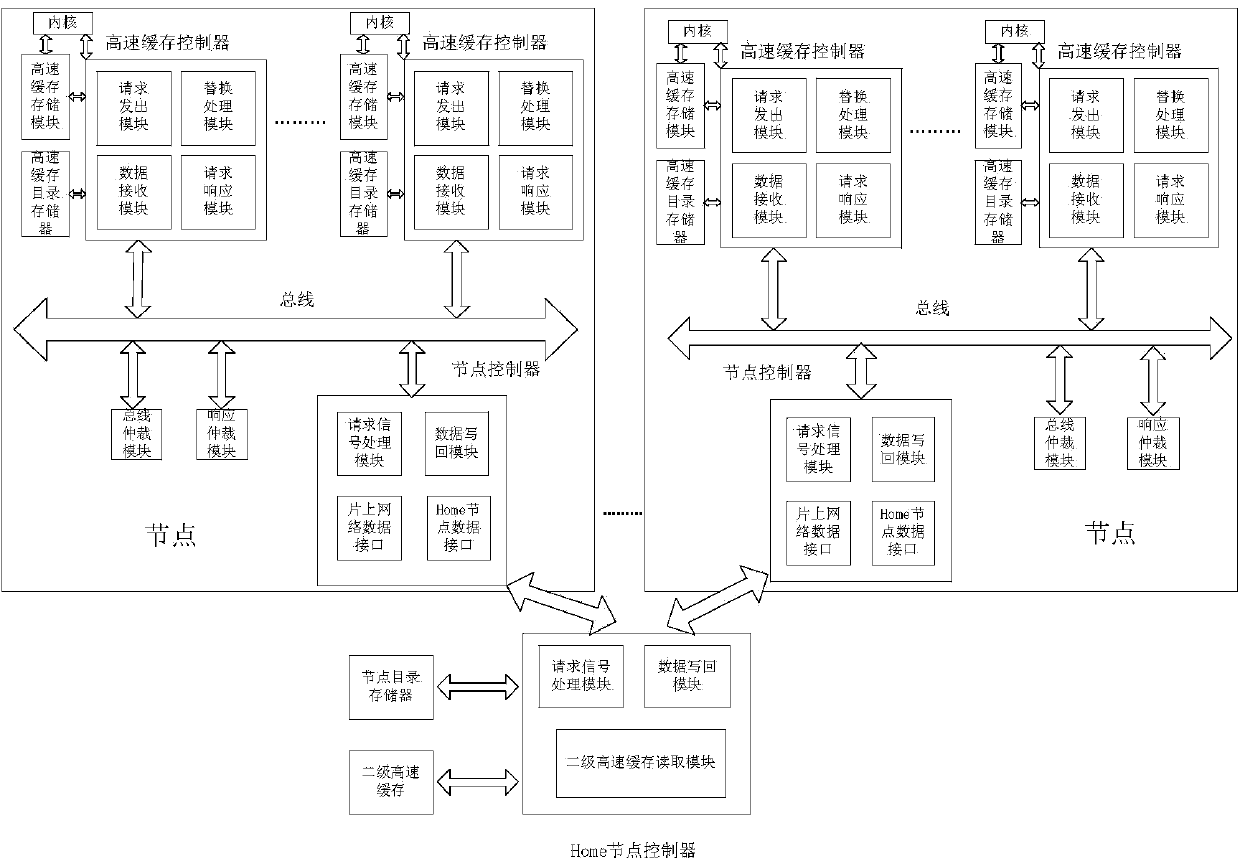

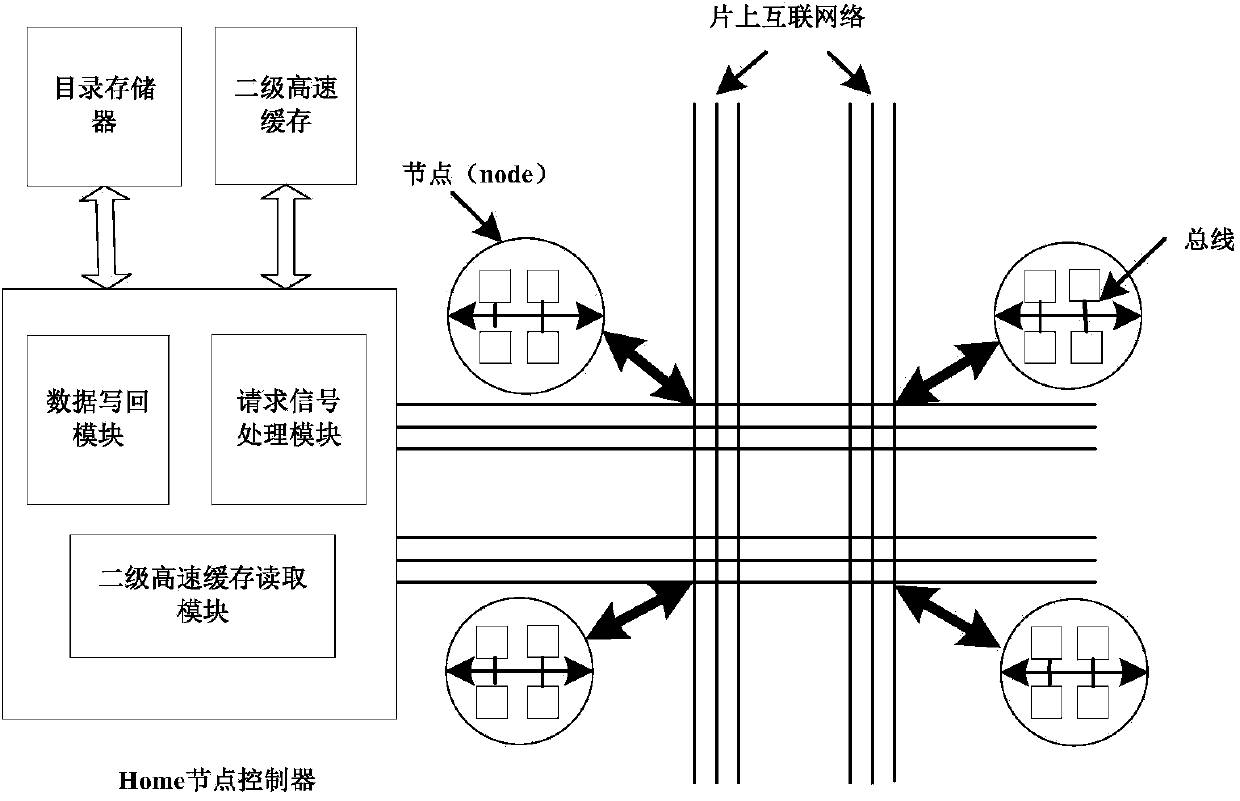

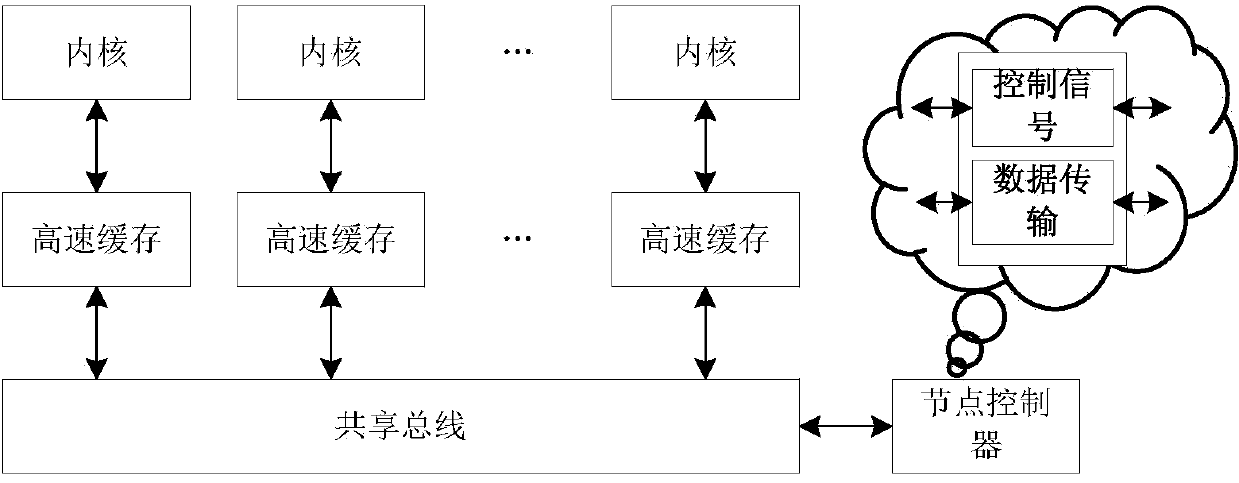

[0046] Such as Figure 1~4 As shown, the present invention is a layered system for implementing a cache coherency protocol. There are multiple cores in the system, and the multiple cores are divided into several groups, and each group serves as a node, which is the first node of the system. One layer; between the nodes is the second layer of the system; the node is provided with a node controller, one end of the node controller is connected to the home node controller, and the other end of the home node controller One end is respectively connected with the node directory storage and the second-level cache.

[0047] It should be noted that each core in the node is also connected to a cache controller;

[0048] A cache storage module, one end is connected to the core, and the other end is connected to the cache controller;

[0049] a cache directory storage connected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More