Novel semiconductor packaging method

A packaging method and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., to achieve strong support, good thermal shock resistance and water vapor shock performance, and low impedance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] In order to make it easier for those skilled in the art to understand the technical content of the present invention, the present invention will be further described in detail below in conjunction with the embodiments and accompanying drawings.

[0058] The semiconductor packaging method disclosed in the present invention comprises the steps of:

[0059] (1) Provide a wafer with a functional area 101 and a substrate, each chip 100 of the wafer is provided with a metal contact 102;

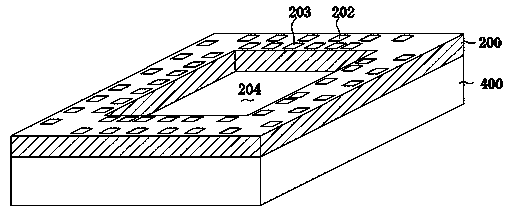

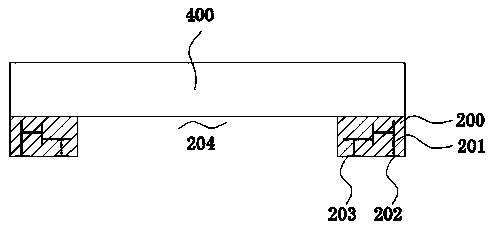

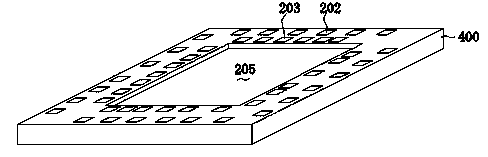

[0060] (2) The substrate may be a multi-layer substrate or a single-layer substrate, such as a glass substrate or a printed circuit board. Such as figure 1 and 2As shown, it is a two-layer substrate composed of a glass substrate 400 and a printed circuit board 200. Metal pads are made on the same side of the substrate, and the metal pads include an inner ring metal pad 203 and an outer ring metal pad 202. The ring metal pad 203 corresponds to the position of the metal contact 102 on the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More