United simulation tool suitable for multi-type CPU

A co-simulation and tool technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as increasing work complexity and workload, and achieve the effect of simplifying work and improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

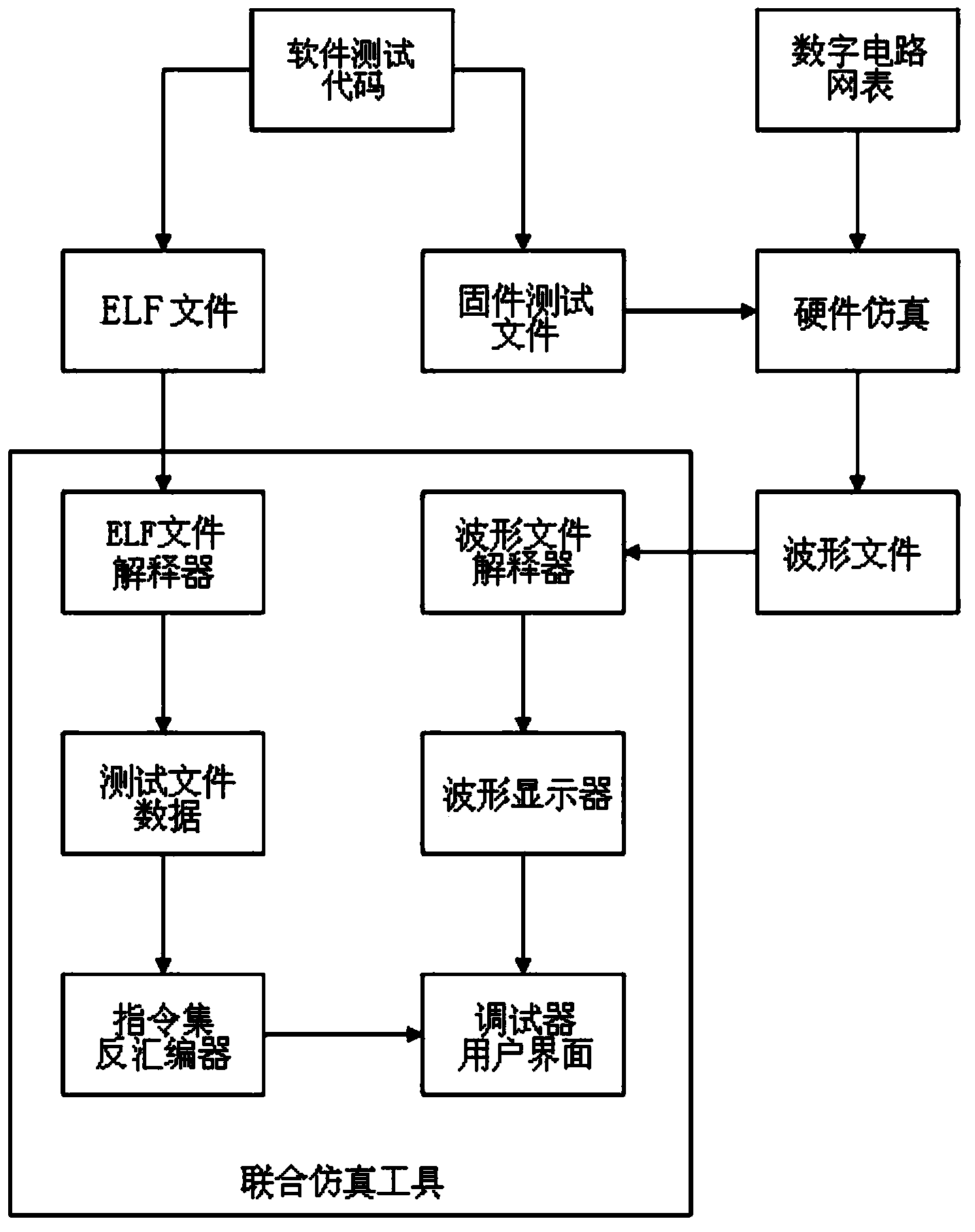

[0014] As shown in the accompanying drawings, the co-simulation tool applicable to multiple types of CPUs includes: an ELF file interpreter, an instruction set disassembler, a waveform file interpreter, a waveform display, and a debugger user interface. The co-simulation tool has the function of displaying the graphical interface (that is, the user interface of the debugger), the function of displaying the waveform, and the function of bidirectional automatic correlation between the waveform and the kernel assembly instruction code. The co-simulation tool supports multiple types of CPU cores, such as C51 and ARM; the CPU core type can be selected through the debugger user interface. The co-simulation tool supports floating and embedding of each sub-window in the multi-document view.

[0015] Software test code is the software code written by software testers for further debugging of the circuit. The software test code is compiled by a compiler based on different kernels to ge...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More