Chip packaging structure with cavity and packaging method thereof

A technology of chip packaging structure and packaging method, which is applied in the fields of electric solid-state devices, semiconductor devices, semiconductor/solid-state device manufacturing, etc., can solve the problems of unsatisfactory performance requirements and reliability, heat dissipation and power distribution, etc., and achieve excellent heat dissipation and production The process is simple and advanced, and the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

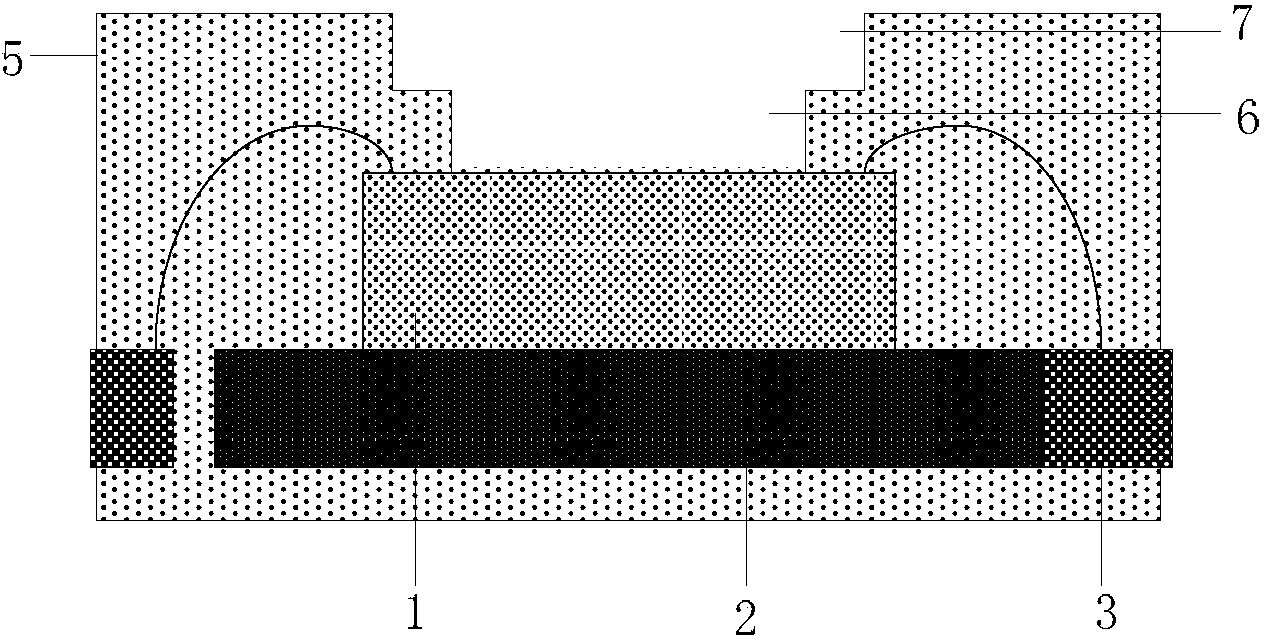

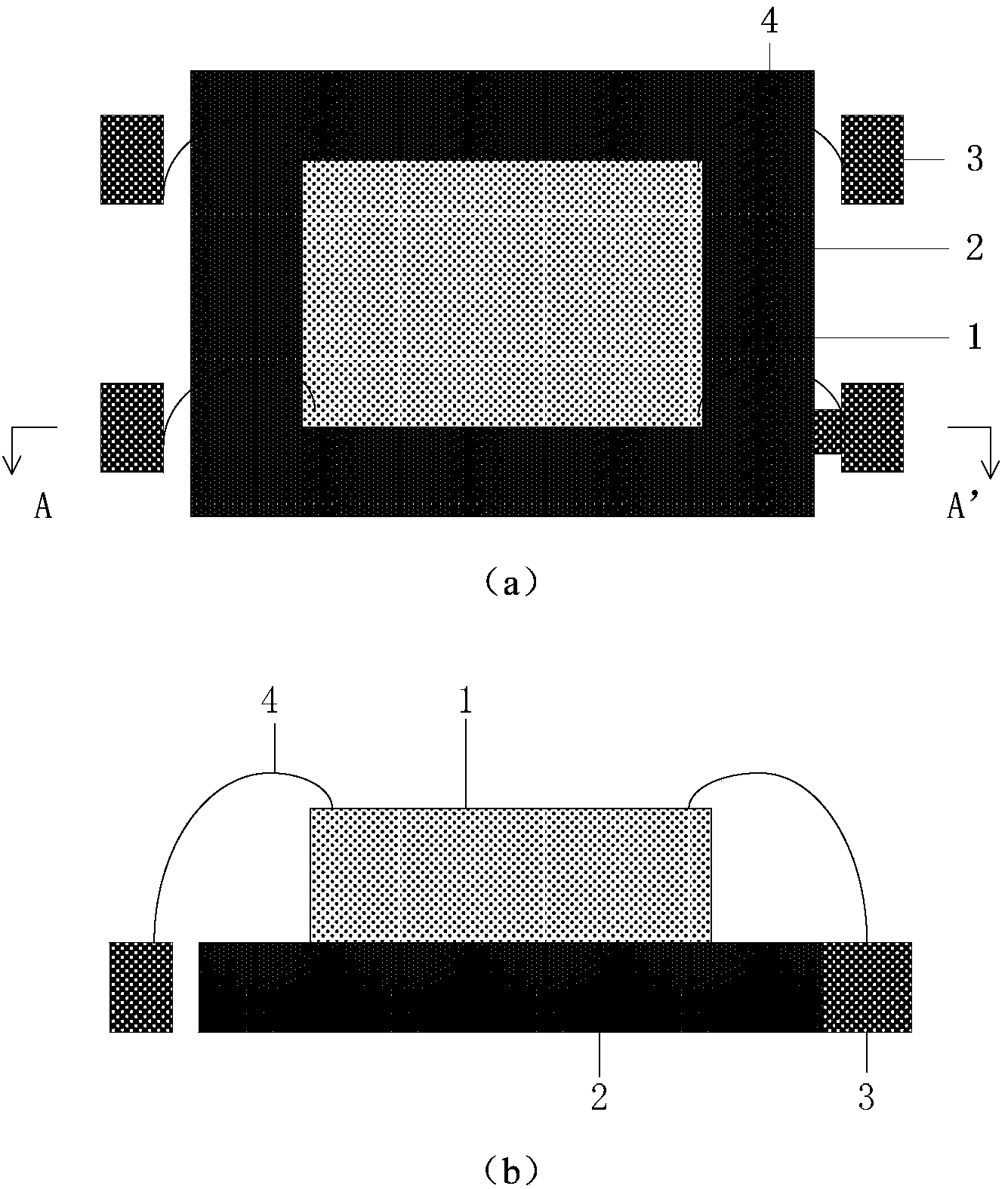

[0034] Such as figure 1 As shown, the chip packaging structure of the present embodiment includes: a chip 1, a substrate 2, a lead frame 3, a wire 4 and a plastic package 5; wherein, the lower surface of the chip 1 is pasted on the substrate 2; The foot frame 3 is connected; the plastic package body 5 packages the chip 1, the lead frame 3 and the substrate 2, and exposes the lead frame 3 on the side of the plastic package body 5; the upper surface of the chip is provided with a stress structure, and the plastic package body 5 and the chip 1 A cavity 6 is opened on the corresponding part of the upper surface, so that the upper surface of the chip is not in contact with the plastic package; and a through hole 7 is opened between the cavity 6 and the upper surface of the plastic package 5, so that the upper surface of the chip is not covered by the plastic package , to ensure that the stress of the chip is not affected, and it is connected with the outside world, which is conduci...

Embodiment 2

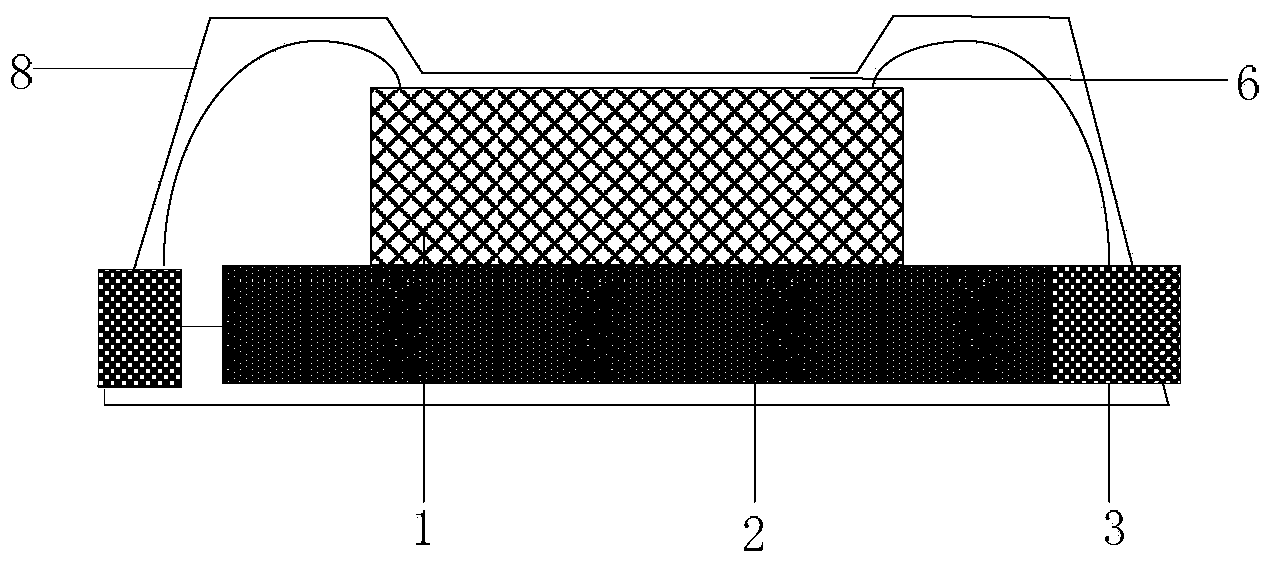

[0043] The chip packaging structure of this embodiment includes: chip 1, substrate 2, lead frame 3, lead 4, plastic package body 5 and sealing film 8; Wherein, the lower surface of chip 1 is pasted on the substrate 2; The lead frame 3 is connected; the sealing film 8 wraps the chip, the lead frame and the substrate, and exposes the bottom surface or side of the lead frame, and seals the sealing film and the edge of the lead frame, thereby forming a cavity between the plastic package and the chip 6, such as image 3 As shown; the plastic package is packaged outside the sealing film, and the lead frame that is not wrapped by the sealing film is exposed on the bottom surface or side of the plastic package; there is a through hole 7 between the plastic package 5 and the sealing film 8 corresponding to the sensitive part, Such as Figure 4 shown.

[0044]In this embodiment, the plastic package body 5 is made of epoxy resin; the sealing film 8 is made of polyester film, the cost i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More