Oscilloscope having delayed trigger function

An oscilloscope and delay time technology, applied in the direction of digital variable display, etc., to achieve the effects of precise delay time, diversified trigger methods, and improved trigger accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

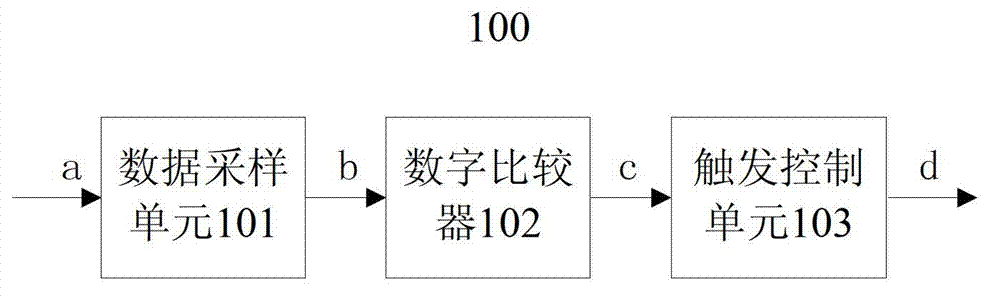

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

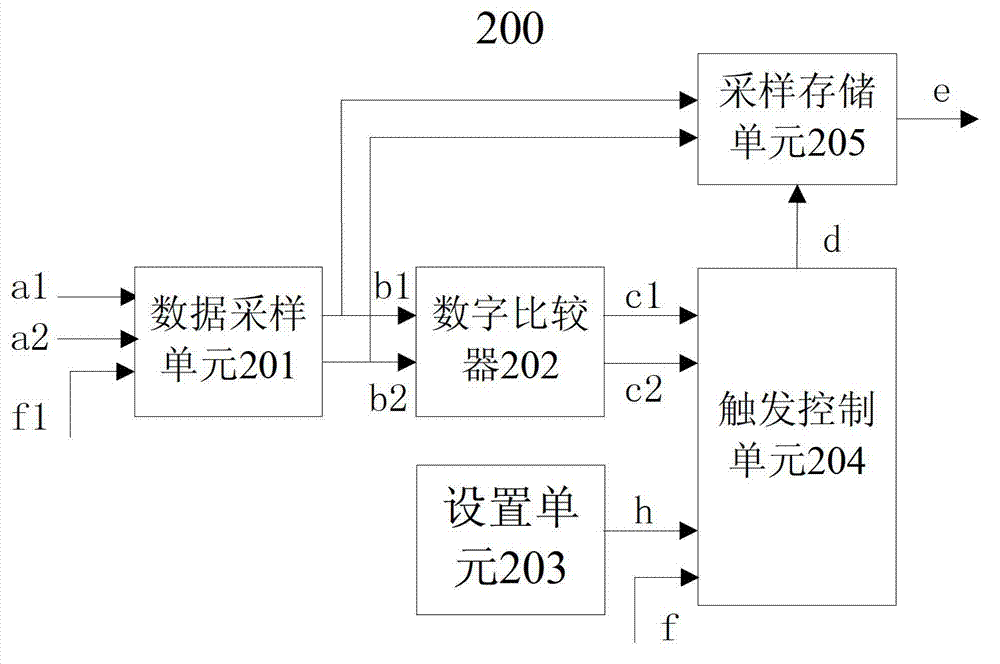

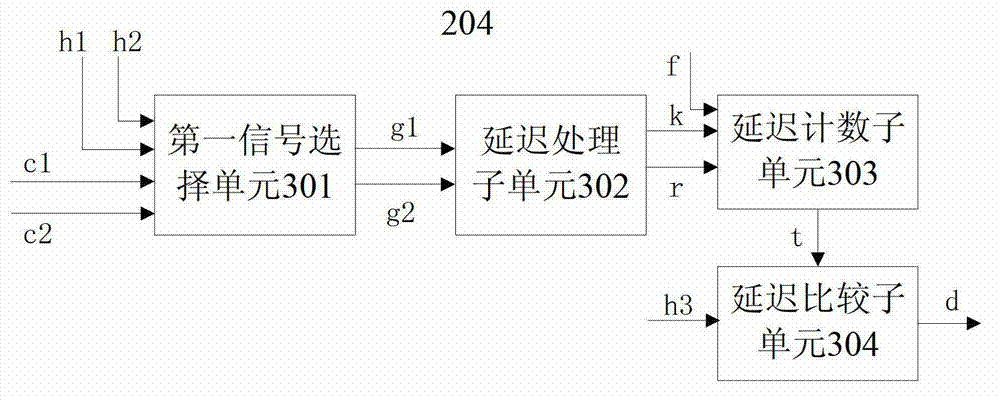

[0092] refer to figure 2 , the data sampling unit 201 includes two ADCs, according to the sampling clock f1, samples the two-way measured signals a1 and a2 respectively, and generates one-way first sampling data b1 and one-way second sampling data b2; the digital comparison unit 202 includes two The digital comparator performs level comparison processing on one channel of first sampled data b1 and one channel of second sampled data b2 to generate corresponding one channel of first comparison signal c1 and one channel of second comparison signal c2; at this time, the clock f is Sampling the clock f1, the trigger control unit 204 obtains the delay time t from the first comparison signal c1 and the second comparison signal c2 according to the sampling clock f1, delay order and edge type. It can be seen that when the data sampling unit 201 samples a channel of the signal to be tested and generates a channel of serial low-speed sampling data, for example, the sampling clock is 125...

example 2

[0100] refer to figure 2 , the data sampling unit 201 samples the two-way measured signals a1 and a2 respectively according to the sampling clock f1 to generate parallel n-way first sampling data b1, parallel n-way second sampling data b2 and a trigger clock f2; The comparison unit 202 performs level comparison processing on n channels of first sampling data b1 and n channels of second sampling data b2, respectively, to generate parallel n channels of first comparison signals c1 and parallel n channels of parallel second comparison signals c2; at this time, The clock f is the trigger clock f2, and the trigger control unit 204 obtains the delay time t from the parallel n-way first comparison signal c1 and the parallel n-way second comparison signal c2 according to the trigger clock f2, the delay sequence and the edge type .

[0101] In the second example, the sampling clock f1 may include M sampling clocks f1 (1~M) with the same frequency and different phases, and the data sa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More