Analog circuit fault diagnosis method based on cascade connection integrated classifier

A fault diagnosis and classifier technology, applied in the direction of instruments, measuring electricity, measuring electrical variables, etc., can solve problems such as difficult to distinguish

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

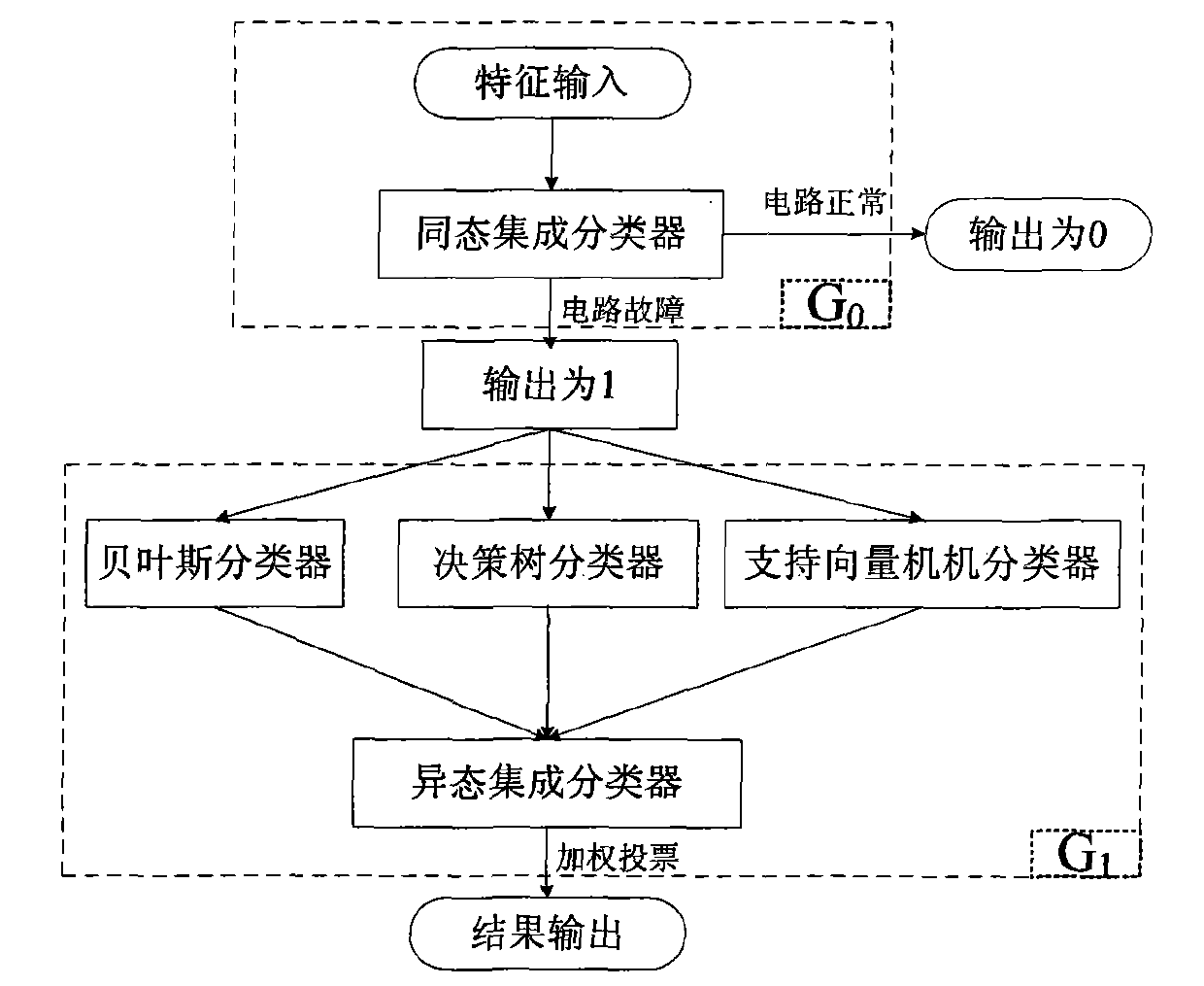

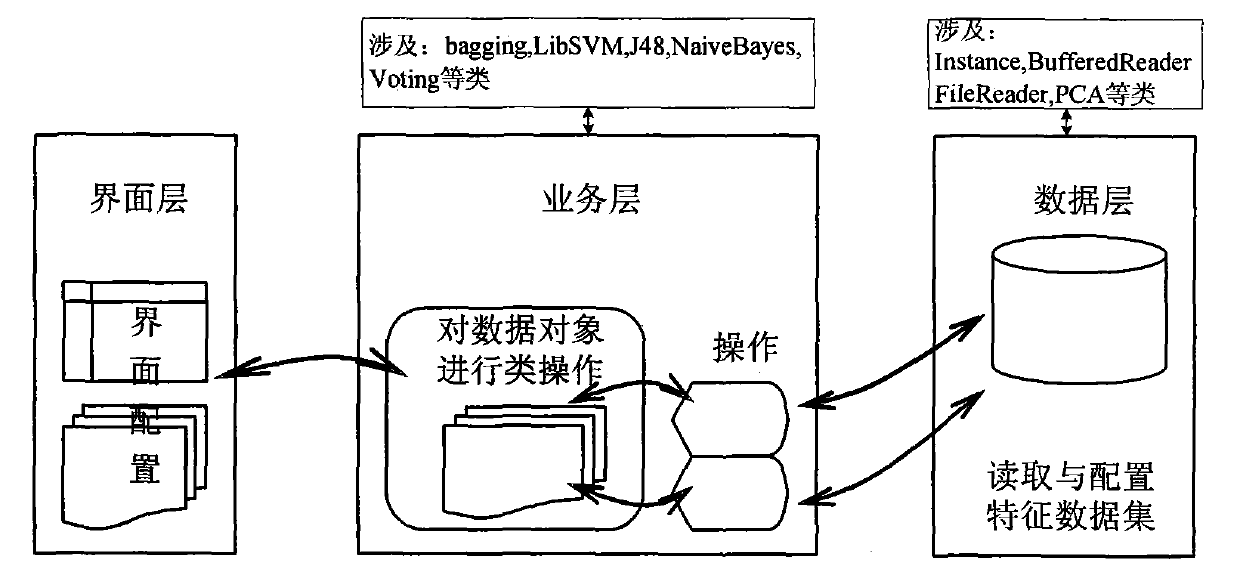

[0007] Knowledge-based analog circuit fault diagnosis technology is essentially a pattern recognition and classification problem. Therefore, how to extract effective features of faults is a key technology and an important part of analog circuit fault diagnosis. At the same time, the ultimate purpose of extracting features is to construct a classifier for test samples and realize correct classification and identification of different fault types. Ultimately, to achieve this goal and complete the real realization of fault diagnosis, it is necessary to implement software for the algorithm.

[0008] In order to achieve the above object, method of the present invention is achieved like this:

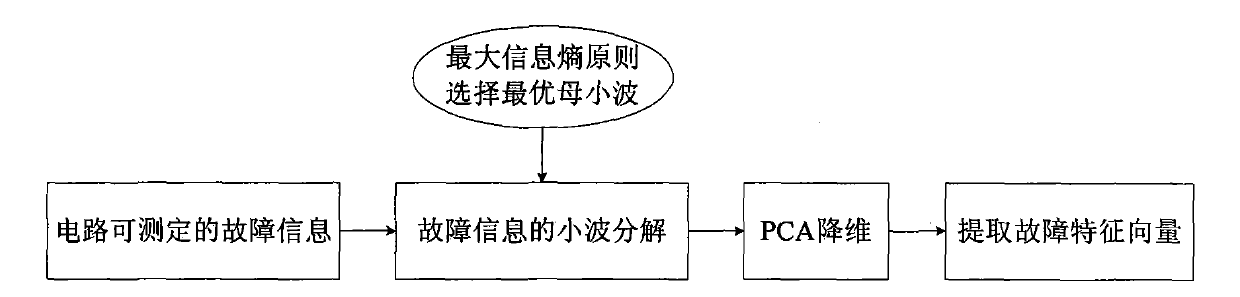

[0009] 1. Optimal wavelet extraction of analog circuit fault feature information

[0010] The wavelet fault feature information extraction method as a signal processing is a current research hotspot. Wavelet analysis belongs to multi-resolution analysis, which is a fine time-frequency analys...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More