Parallel and serial data converting circuit based on FPGA

A technology for converting circuits and serial data, applied in the field of parallel-serial data conversion circuits, can solve the problems of increasing cost, inconvenient circuit design, and limiting low-end FPGA applications, and achieves the effect of high applicability and convenient circuit design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings.

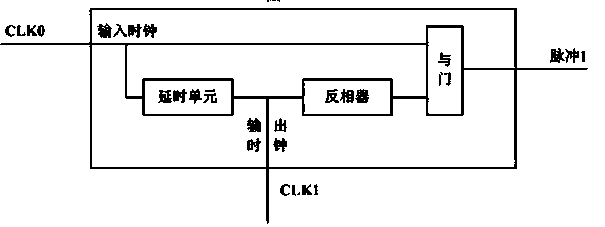

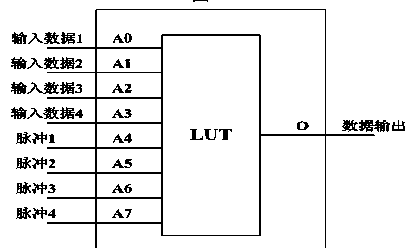

[0021] The present invention provides an FPGA-based parallel-to-serial data conversion circuit, which is composed of a data output selector and a pulse generation unit. The specific implementation structure is as follows figure 1 shown. figure 1 The parallel-to-serial data conversion circuit shown can convert 4-bit parallel data into serial output; according to user needs, the pulse generation unit can be expanded to realize parallel-to-serial data conversion with any bit width. The present invention takes figure 1 The circuit shown is taken as an example to illustrate a specific implementation. The structure of each part is described in detail below:

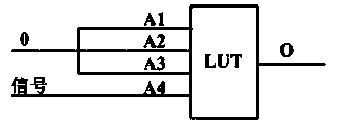

[0022] Data selectors such as figure 1 As shown, it is a 4-to-1 selector. Parallel data is output as serial d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com