Capacitor and power integrated circuit

A capacitor and electrical connection technology, applied in the field of power device structure design, can solve the problems of large power integrated circuits and high production costs, and achieve an effect that is conducive to popularization and application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

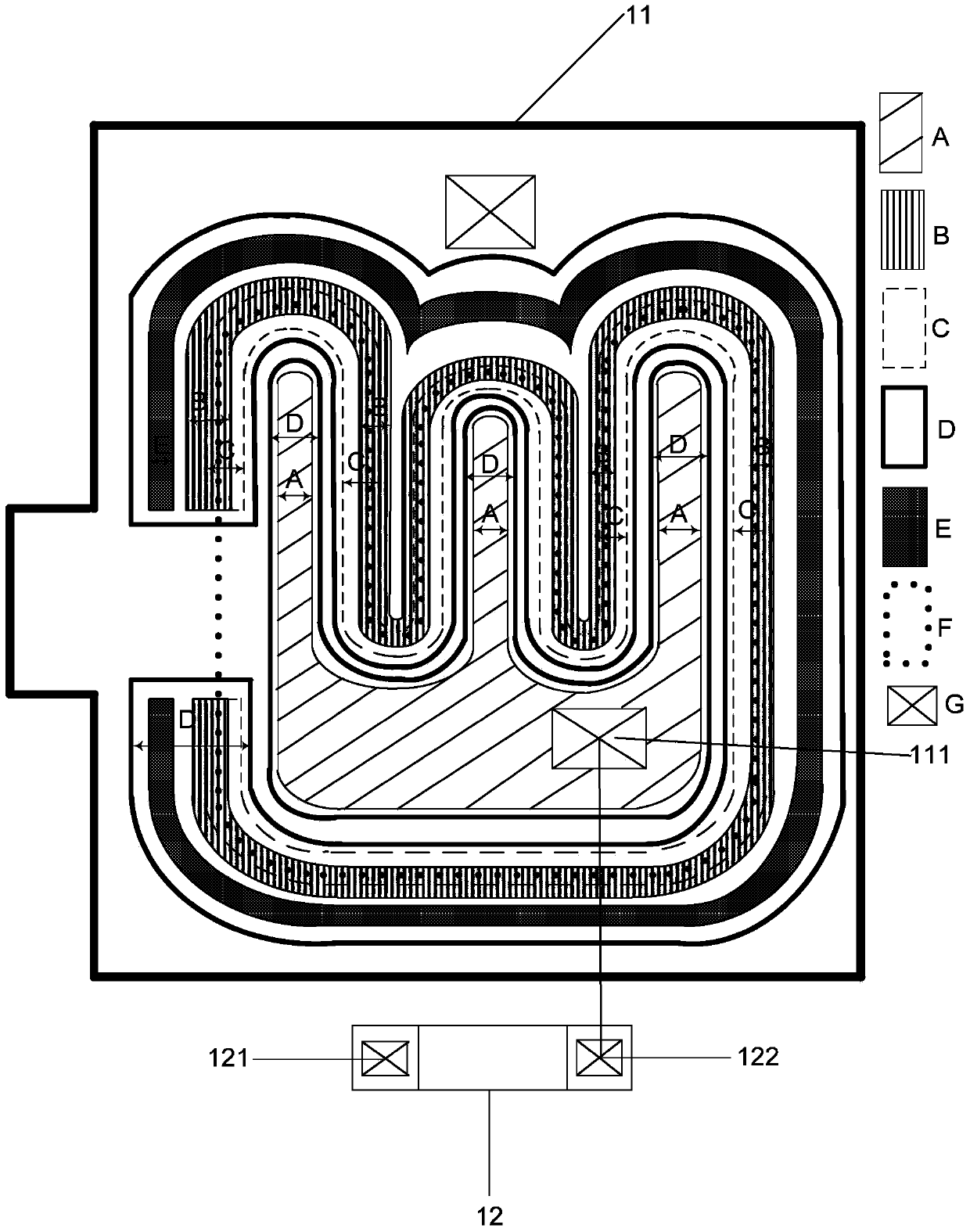

Embodiment 1

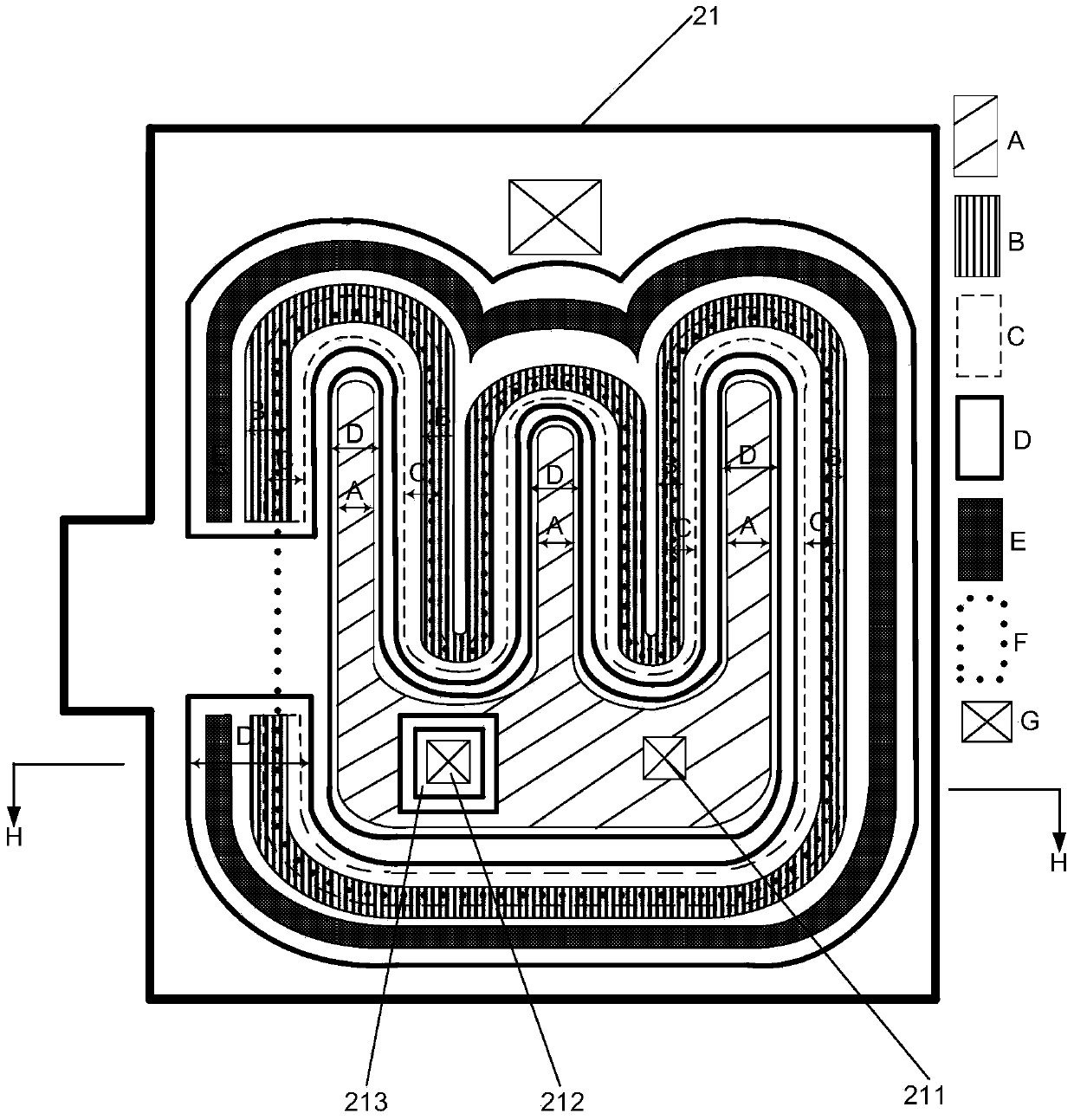

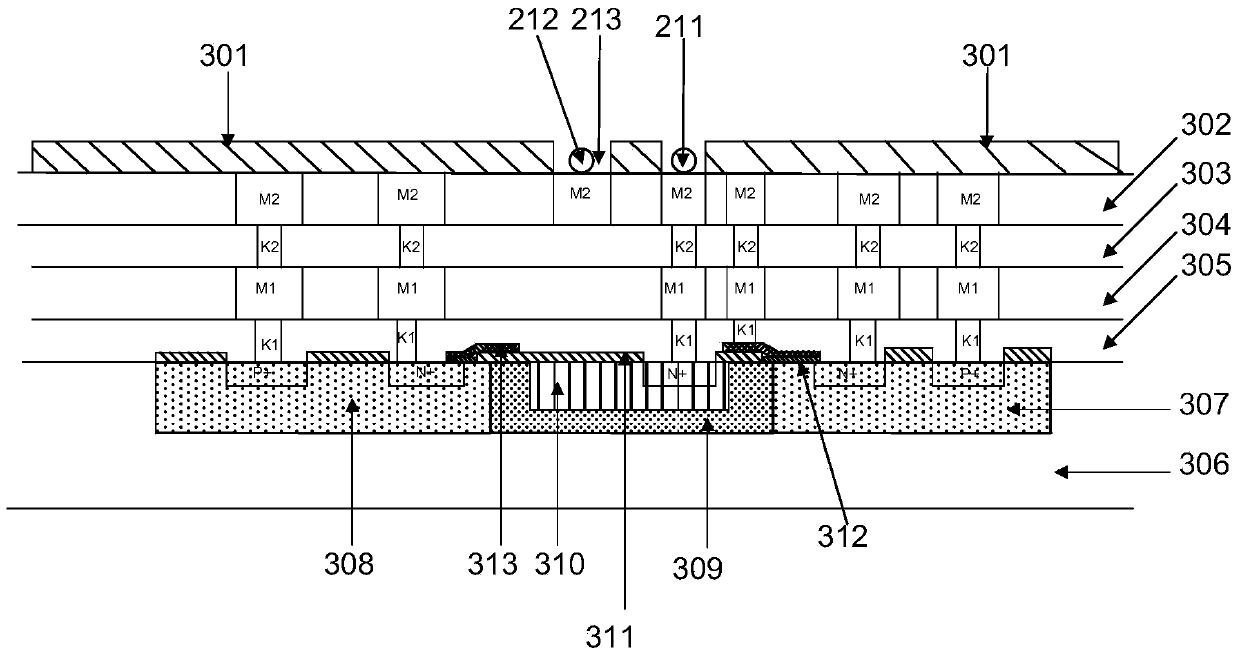

[0014] Embodiment 1 of the present invention provides a field effect transistor, the field effect transistor is an NLDMOS transistor, such as figure 2 as shown, image 3 yes figure 2 The H-H sectional view of the figure shows only the parts related to Embodiment 1 of the present invention for the convenience of description.

[0015] Among them, graph A represents the low-voltage N well region of NLDMOS transistor 21, graph B represents the N+ doped region of NLDMOS transistor 21, graph C represents the POLY polycrystalline layer of NLDMOS transistor 21, graph D represents the top layer metal M2, and graph E represents the NLDMOS transistor The P+ doped region of 21 , the graph F represents the high voltage N well region of the NLDMOS transistor 21 , and the graph G represents the pin PAD of the NLDMOS transistor 21 . combine figure 2 with image 3 As shown, in Embodiment 1 of the present invention, the NLDMOS transistor 21 includes a passivation layer 301 and a P substr...

Embodiment 2

[0019] Embodiment 2 of the present invention provides a power integrated circuit, including a field effect transistor and a capacitor as described in Embodiment 1 above. The field effect transistor may be the NLDMOS transistor 21 described in Embodiment 1, which will not be repeated here.

[0020] In summary, in the capacitor proposed by the present invention, its lower plate is electrically connected to the drain of the field effect transistor, and the lower plate is a part of the well region that includes the drain, and its upper plate is a portion that includes the drain of the field effect transistor. Part of the well region corresponds to the top layer metal, so that the capacitor is integrated into the field effect transistor without increasing the volume of the field effect transistor. If the field effect transistor integrated with the capacitor is applied to a power integrated circuit, the current integrated capacitor can be reduced. The size of the power integrated ci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com