Non-data-aided parallel clock synchronizing method and system

A technology without data assistance and clock synchronization, applied in the field of communication, can solve the problems of unsuitable multi-path channel environment and long convergence time of Gardner algorithm, so as to meet the processing requirements of high-speed and large data volume, shorten processing delay, The effect of stable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

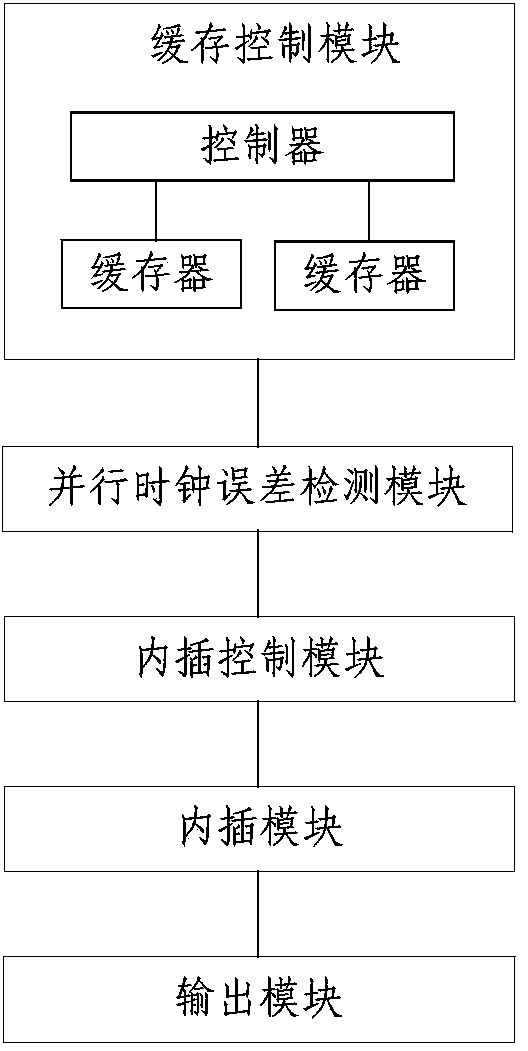

Embodiment 1

[0071] This embodiment is applicable to the wireless burst communication mode, that is, there is a gap between data transmissions, frame header synchronization needs to be completed again for each burst communication, and all states need to be initialized. Assuming that the input data rate is N times the symbol rate, if the symbol period is T, the sampling clock period is T S =T / N; the data length of the segment buffer and the calculation of the sampling clock deviation is M*N; the parallel input data is N P way, parallel output is N P / N way. Parallel input N p After the channel data is interpolated and controlled, the output is N P *K / N channel data. The interpolation algorithm adopts cubic interpolation, and each K-channel input forms a group to obtain one interpolation output. The final output of the parallel interpolator is N P / N way. In this example, N, M, N P , K are all positive integers, set N=4, N P =8, M=512, K=4.

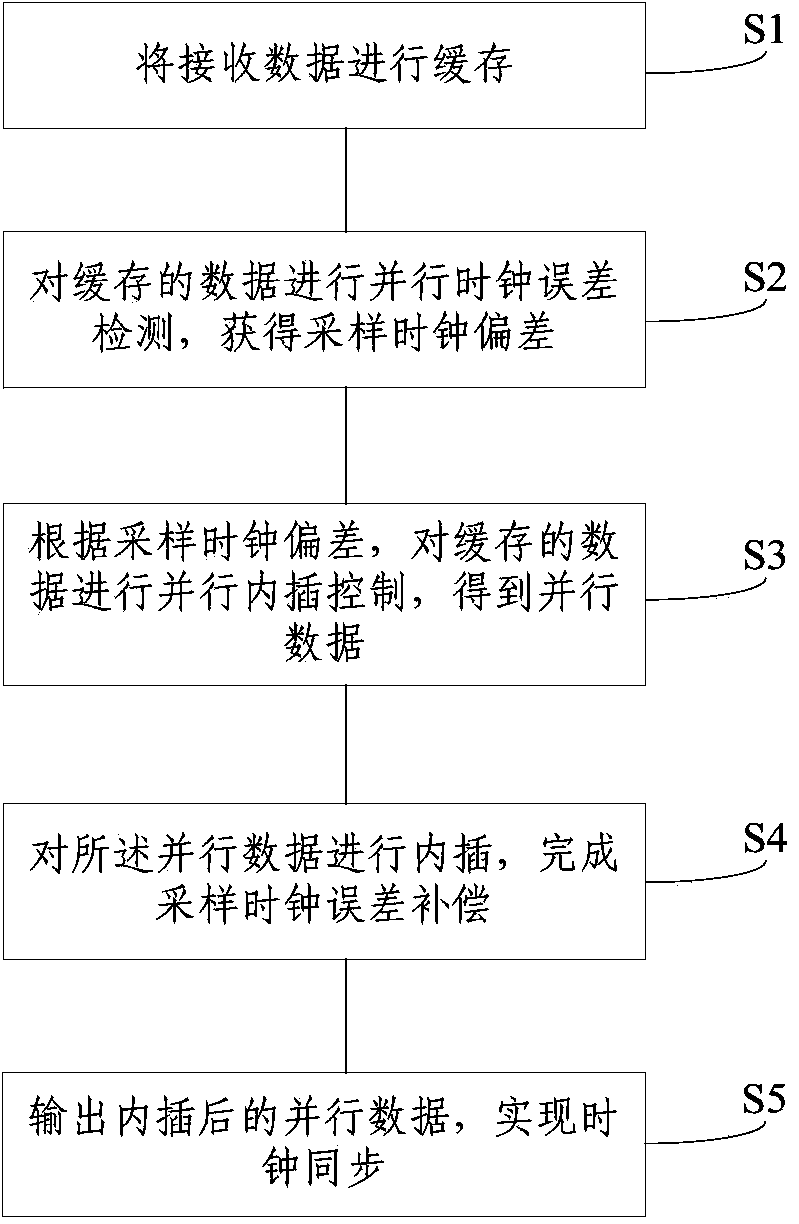

[0072] The non-data-assisted parallel c...

Embodiment 2

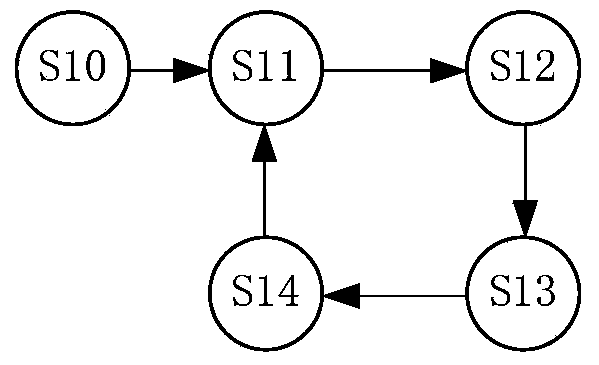

[0097] This embodiment considers a continuous communication mode, that is, data is sent all the time without any initializeable time slot. In this case, if the input data is always in the under-sampling state, when the data is buffered, it needs to be continuously moved backwards from the buffer to ensure the continuity of the data. No matter how big the buffer space is, there will always be a situation where the backward move exceeds the buffer space. In this case, the embodiments for the burst communication mode are no longer applicable.

[0098] In this embodiment, it is still assumed that the rate of the input data is N times the symbol symbol rate, if the symbol period of the symbol is T, the sampling clock period is T S =T / N; the data length of the segment buffer and the calculation of the sampling clock deviation is M*N; the parallel input data is N P way, parallel output is N P / N way. where the input of the interpolation control is N P way, the output is N P *K / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More