Through si via radio frequency test structure and parasitic extracting method thereof

A technology of radio frequency testing and testing structures, which is applied in the direction of single semiconductor device testing, electrical components, electric solid devices, etc. It can solve the problems of difficult removal, multiple de-embedding structures, and large chip area, so as to reduce process costs and improve accuracy. , the effect of small chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

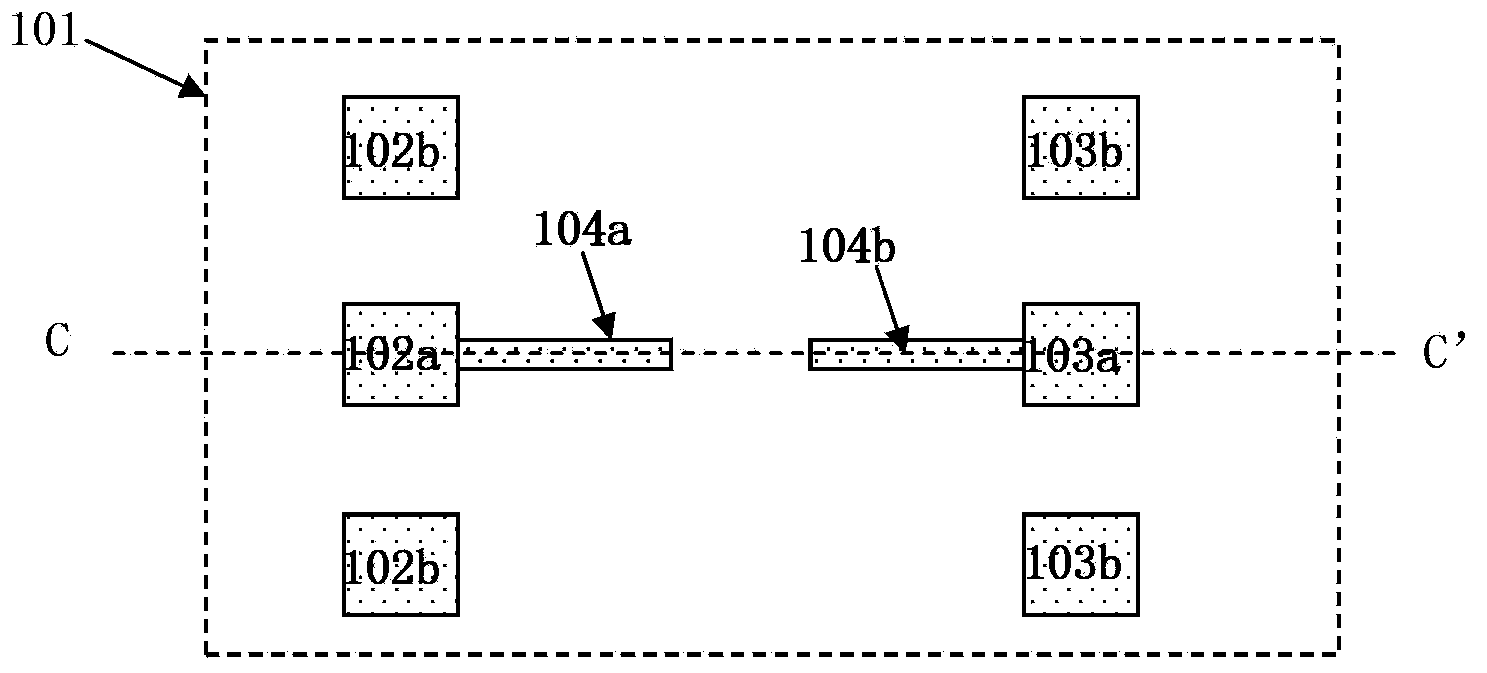

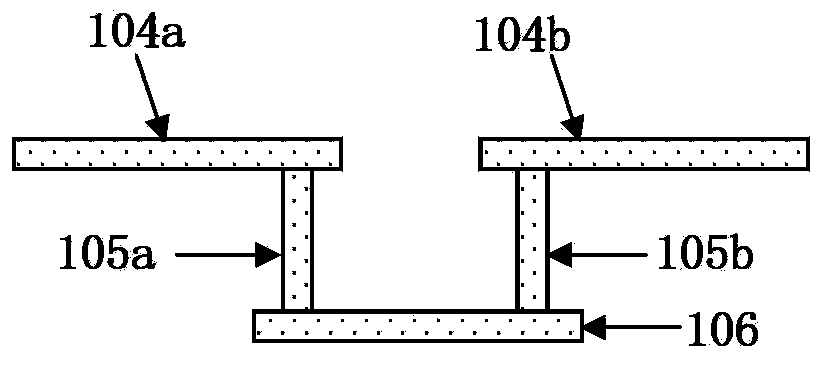

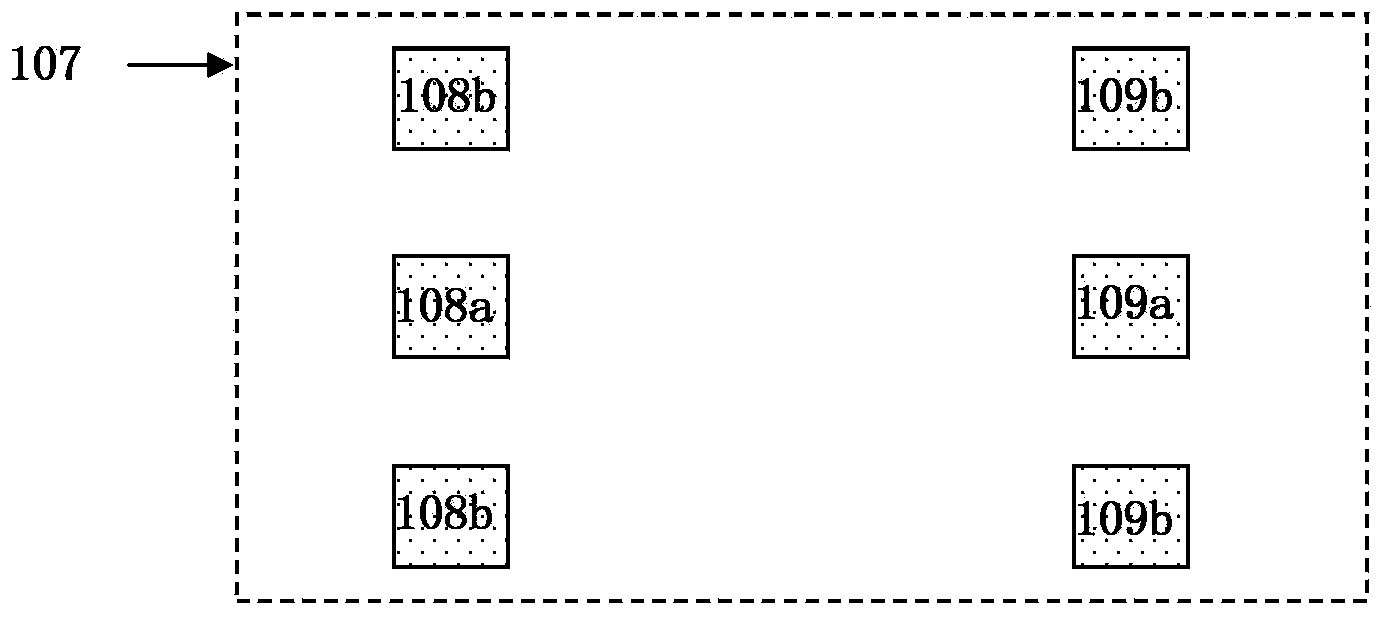

[0032] Such as Figure 2A As shown, it is a top view of the test structure 1 of the radio frequency test structure of the through-silicon via in the embodiment of the present invention; Figure 2B shown, is along the Figure 2A The profile of the line AA' in Figure 2C shown, is along the Figure 2A The section view of the BB' line in ; such as Figure 2D As shown, it is a top view of the open circuit de-embedding structure 2 of the radio frequency test structure of the TSV according to the embodiment of the present invention. The radio frequency test structure of the TSV in the embodiment of the present invention is composed of a test structure one 1 and an open circuit de-embedding structure two 8 .

[0033] The test structure 1 includes port 1 and port 2. The port 1 is composed of a signal terminal 2a and two ground terminals 2b in a ground-signal-ground (GSG) structure; the port 2 is composed of a signal terminal 3a It is composed of two ground terminals 3b in a groun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More