Power-supply clamp ESD circuit

A power supply voltage and clamping technology, which is applied in the direction of circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc. Discharge circuit conduction and other problems, to achieve the effect of ensuring reliability, increasing reliability and good reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

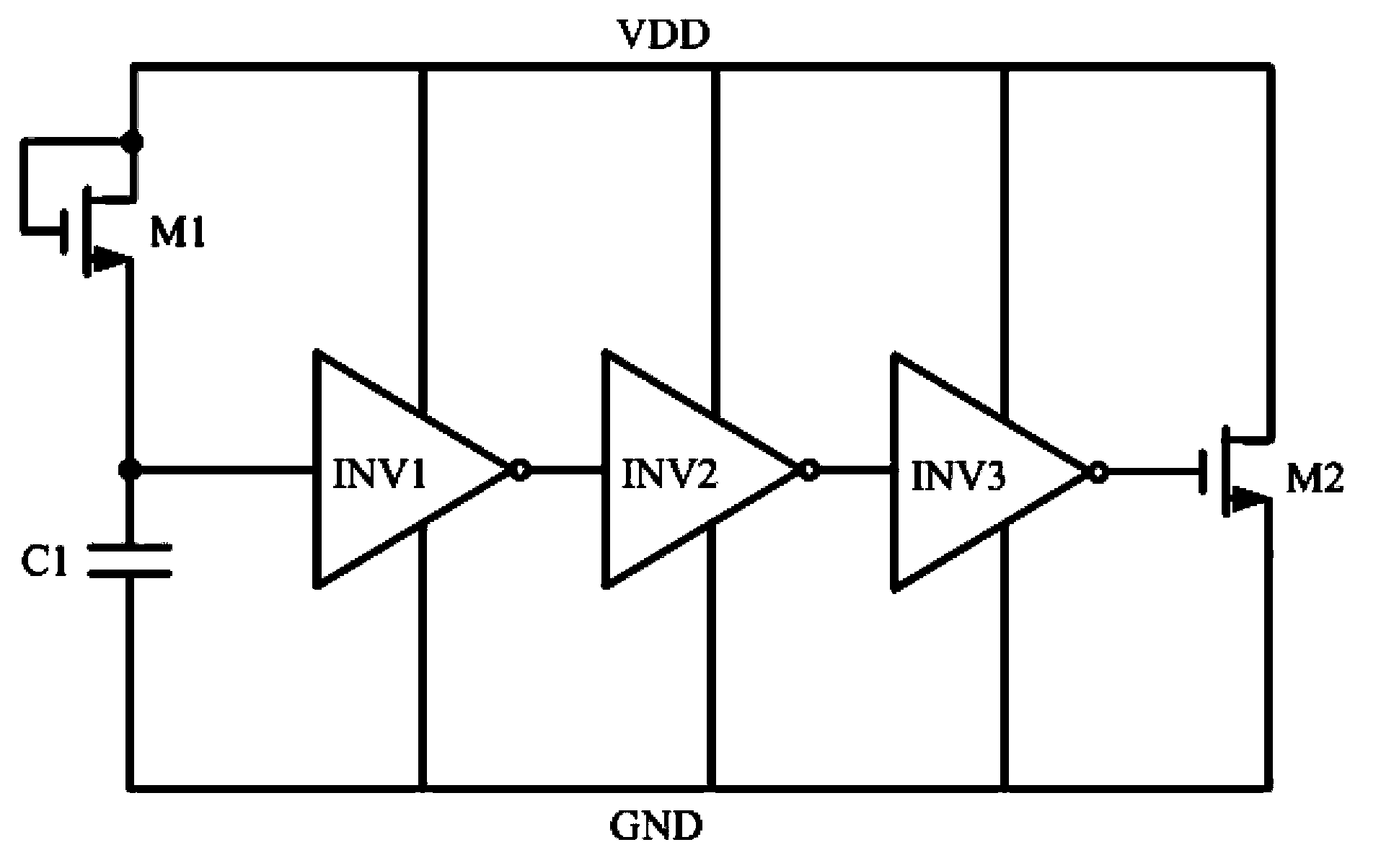

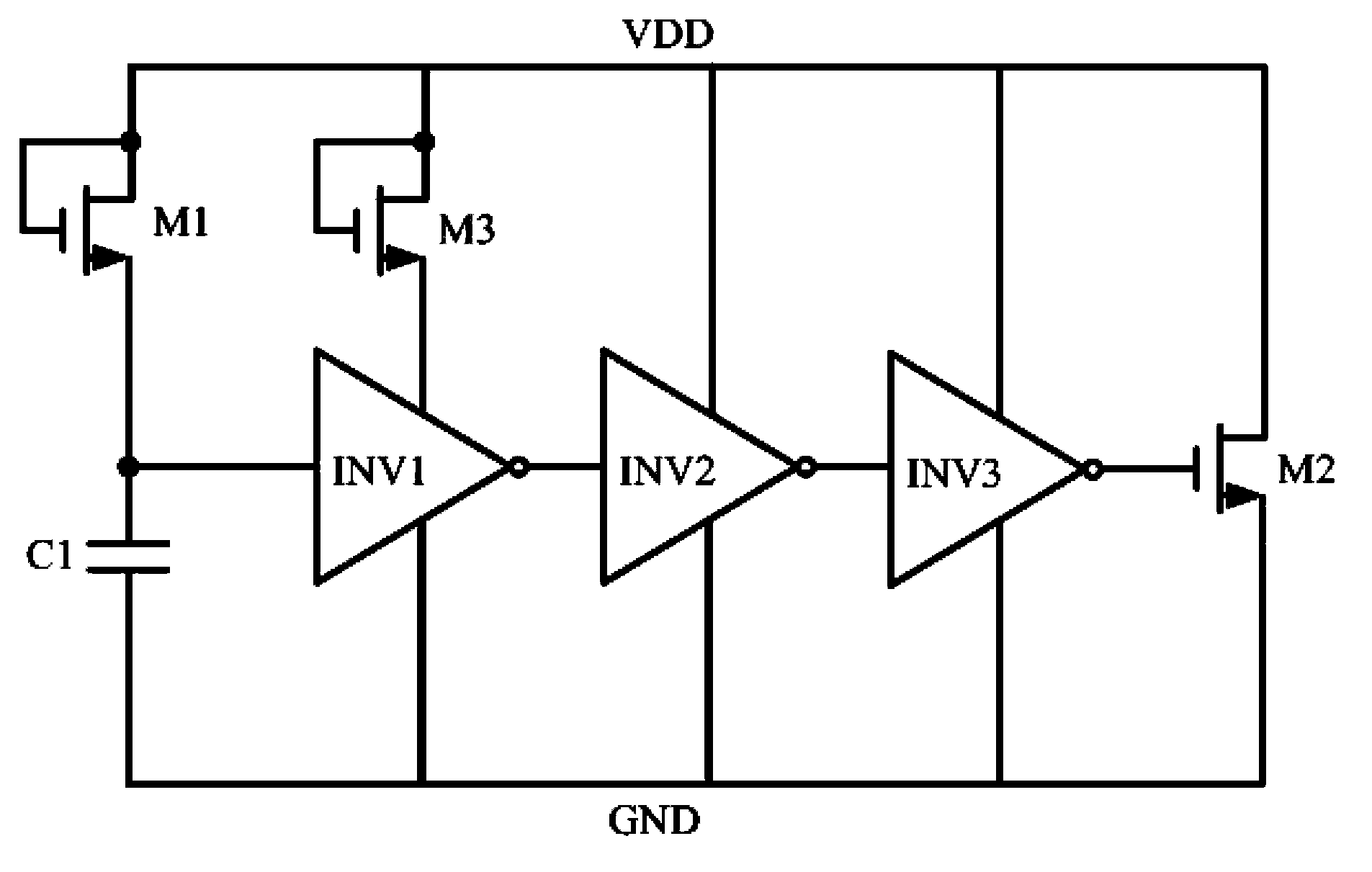

[0020] see figure 2 As shown, in the following embodiments, the power clamp ESD circuit of the present invention includes:

[0021] A detection circuit is composed of a first NMOS transistor M1 and a capacitor. The first NMOS transistor M1 is diode-connected, its gate and drain are connected to the power supply voltage VDD, its source is connected to one end of the capacitor C1, and the other end of the capacitor C1 is grounded to GND.

[0022] A buffer circuit is composed of three series-connected inverters INV1-INV3, wherein the input terminal of the first inverter INV1 is connected to the source of the first NMOS transistor M1 and the connection terminal of the capacitor C1. A diode-connected third NMOS transistor M3 is connected in series between the power supply terminal of the first inverter INV1 and the power supply voltage VDD.

[0023] A discharge circuit is composed of a second NMOS transistor M2, the gate of which is connected to the output terminal of the third ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More