PCIe (Peripheral Component Interface express) bus based channel allocating, releasing, data transmitting method and system

A channel allocation and channel technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of lack of effective management of resource pools, low PCIe bus utilization, high processor occupancy at the sending end and receiving end, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

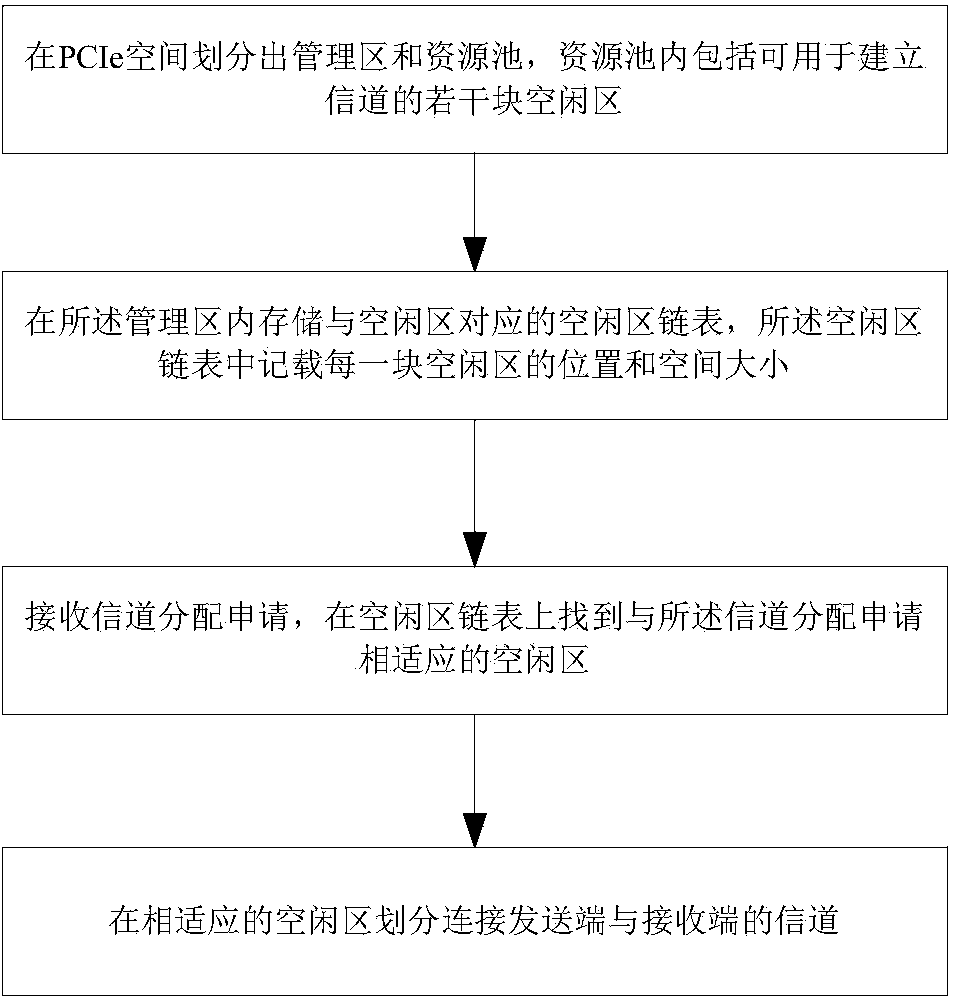

[0101] This embodiment provides a method for channel allocation based on the PCIe bus, such as figure 1 shown, including the following steps:

[0102] S1: Divide a management area and a resource pool in the PCIe space, and the resource pool includes several free areas that can be used to establish channels.

[0103] S2: Store a free area linked list corresponding to the free area in the management area, and record the position and space size of each free area in the free area linked list.

[0104] S3: Receive the channel allocation application, and find the free area corresponding to the channel allocation application in the free area list.

[0105] S4: Divide the channel connecting the sending end and the receiving end in the corresponding idle area.

[0106] In a common PCIe bus-based architecture, RC (root complex) serves as a master control to connect to one EP (end point), or connect multiple EPs through a PCIe bridge chip. RC accesses the address space of the EP memor...

Embodiment 2

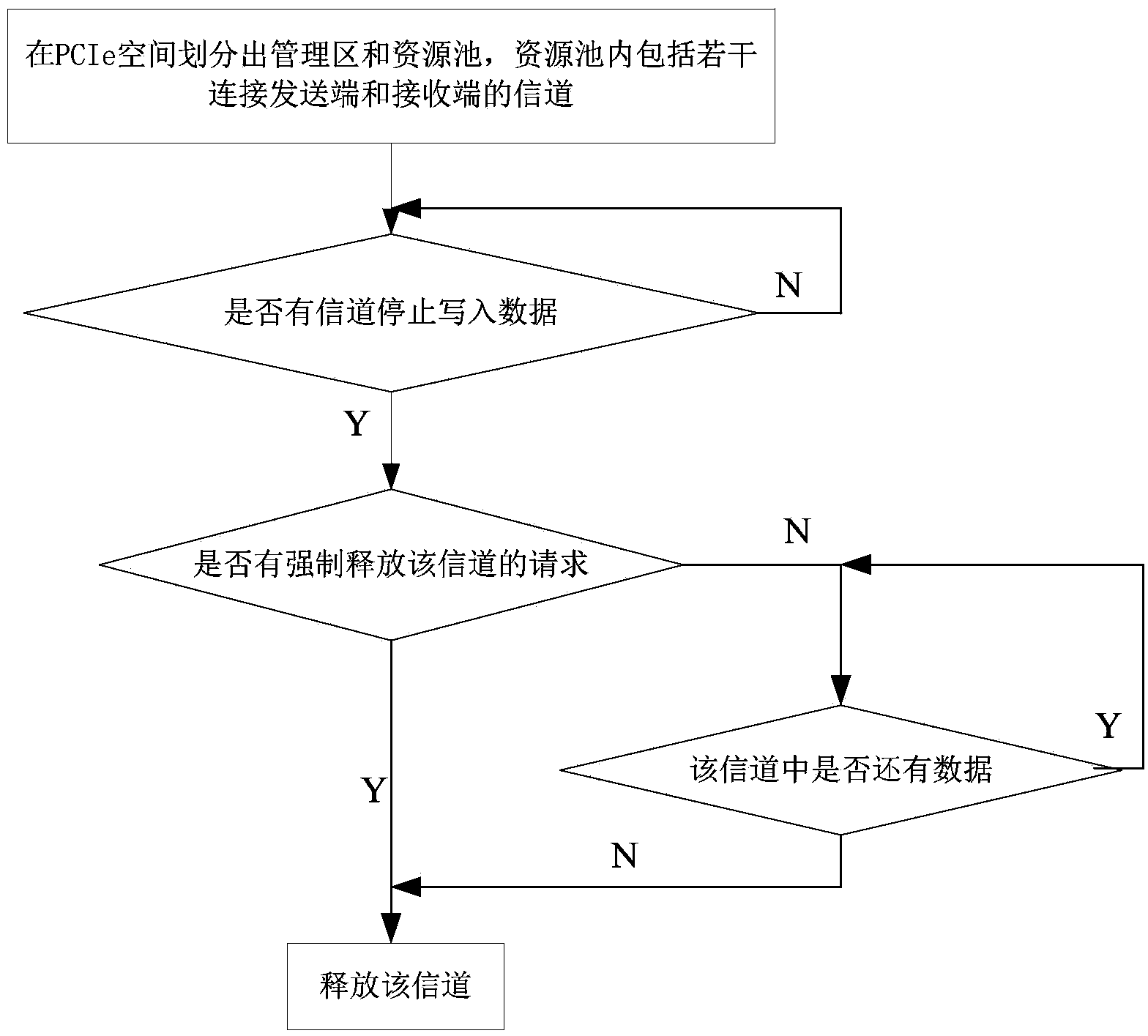

[0128] This embodiment provides a method for channel release based on the PCIe bus, such as figure 2 shown, including the following steps:

[0129] A1: A management area and a resource pool are divided in the PCIe space, and the resource pool includes several channels connecting the sending end and the receiving end.

[0130] A2: Determine whether there is a channel that stops writing data, if so, go to step A3, otherwise repeat this step.

[0131] A3: Determine whether there is a request to forcibly release the channel, if not, proceed to step A4, and if yes, proceed to step A5.

[0132] A4: Determine whether there is data in the channel, if not, go to step A5, if yes, repeat this step.

[0133] A5: Release the channel.

[0134] In the PCIe bus-based channel release method described in this embodiment, when the sending end no longer sends new data, the channel stops reading data, but the data in the channel will continue to be transmitted to the receiving end. The release ...

Embodiment 3

[0144] On the basis of Embodiment 1 and Embodiment 2, the design of the channel state machine is a critical step in the process of channel allocation and release, and it is an indispensable part. The channel creation is initiated at the sending end until the receiving end Sensing this newly created channel and notifying the sender is inseparable from the state machine, including the release of the channel in mandatory and non-mandatory mode, which requires the state machine to coordinate the sending and receiving parties. The notification method can be MSI or through Thread polling. The state machine diagram in the process of channel allocation is as follows: Figure 11 As shown, the state machine diagram in the channel release process is as follows Figure 12 shown.

[0145] This embodiment also provides a design scheme of a channel state machine in a specific application, as follows:

[0146] Channel status includes the following:

[0147] CHANNEL_FREE,

[0148] CHANNEL...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More