System and method for performing SRAM write assist

A technology of write assistance and bit lines, applied in the field of write assistance, can solve the problem that SRAM storage elements cannot be written reliably

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

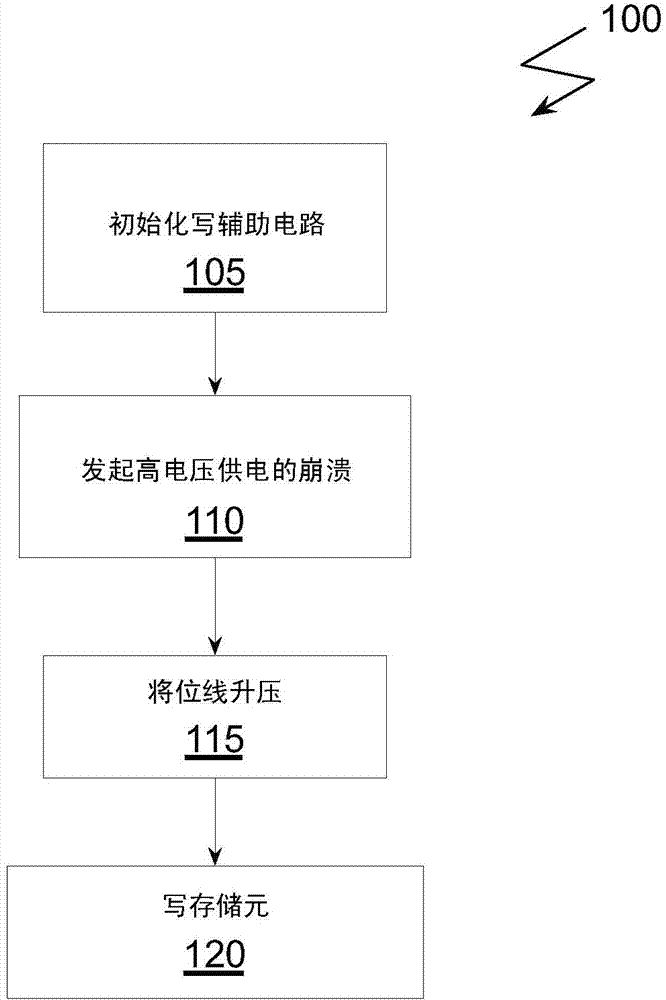

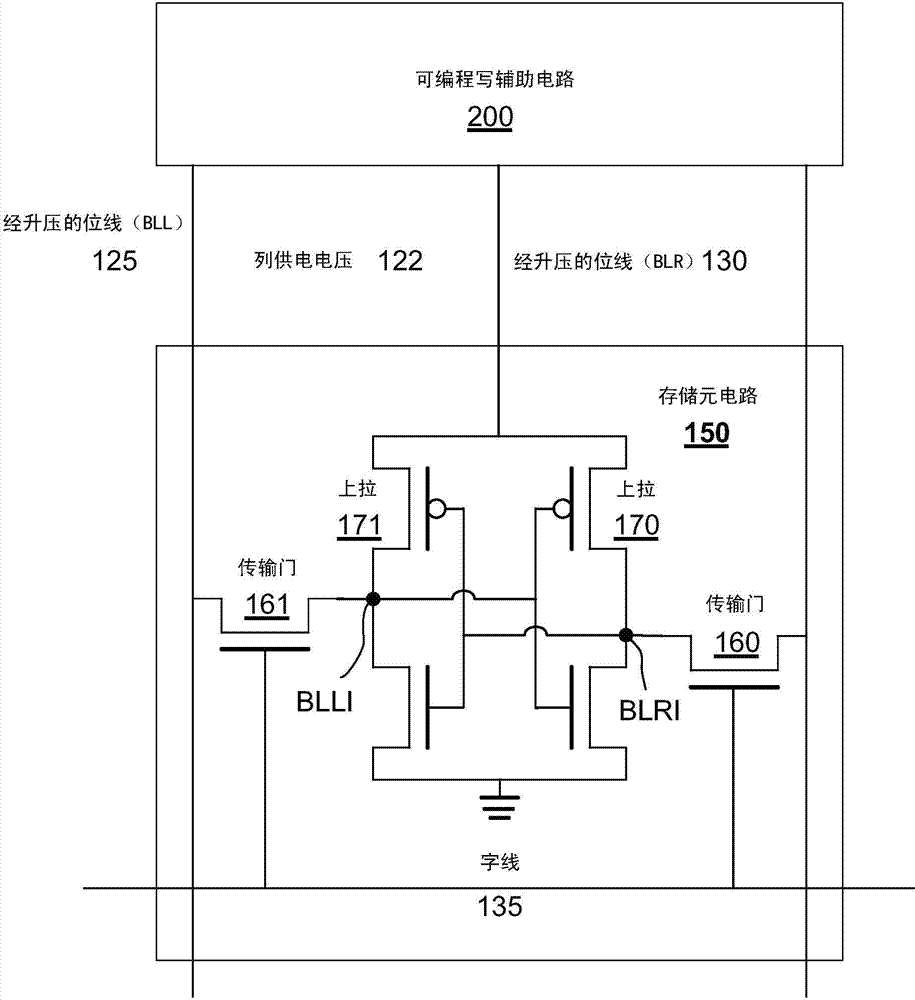

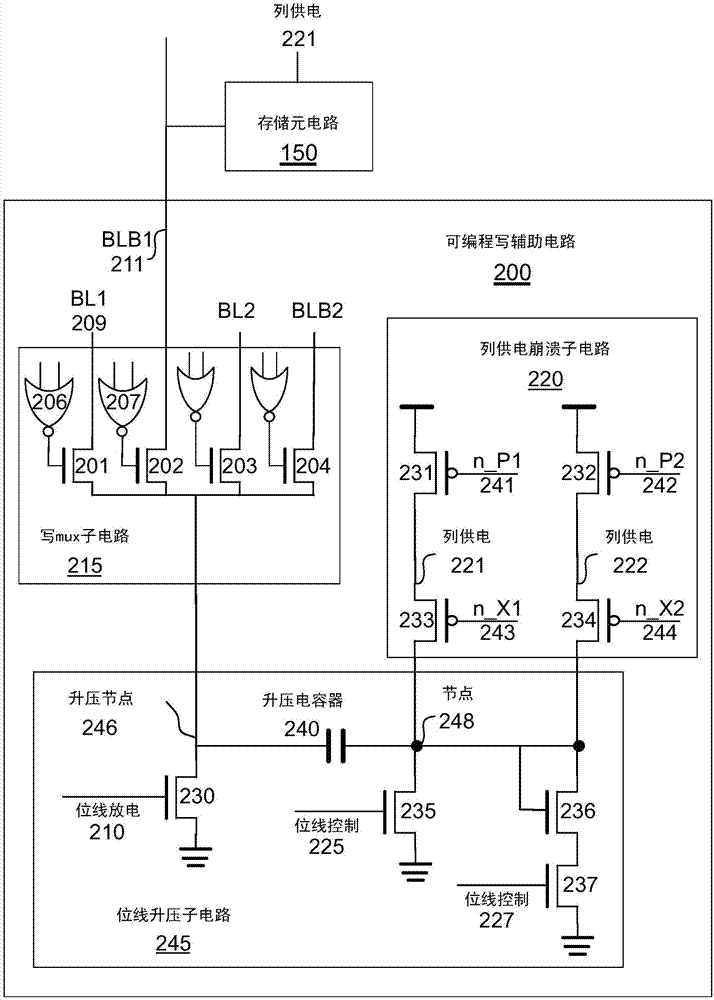

[0015] As previously explained, changes in circuit characteristics can strengthen the PMOS pull-up transistors and weaken the NMOS transmission gates of the memory elements, making the memory cells unreliably writable. Unfortunately, changing the size of the PMOS pull-up transistors to weaken the PMOS pull-ups and changing the size of the NMOS pass-gate transistors to strengthen the NMOS pass-gates is not an effective technique for improving write reliability. For example, when a memory cell is implemented using a Fin-FET (Fin-FET), the size of the memory cell is quantified based on the number of fins. This means that for various design reasons, transistor sizing is not an effective technique for improving write reliability even with minimal changes in circuit characteristics. The write assist weakens the PMOS pull-up transistor and strengthens the NMOS pass gate to improve write reliability without relying on changing the size of the transistor. Write assist is enabled durin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More