Automatic layout method for positions of heat through holes in 3D integrated circuit

An integrated circuit and automatic layout technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings.

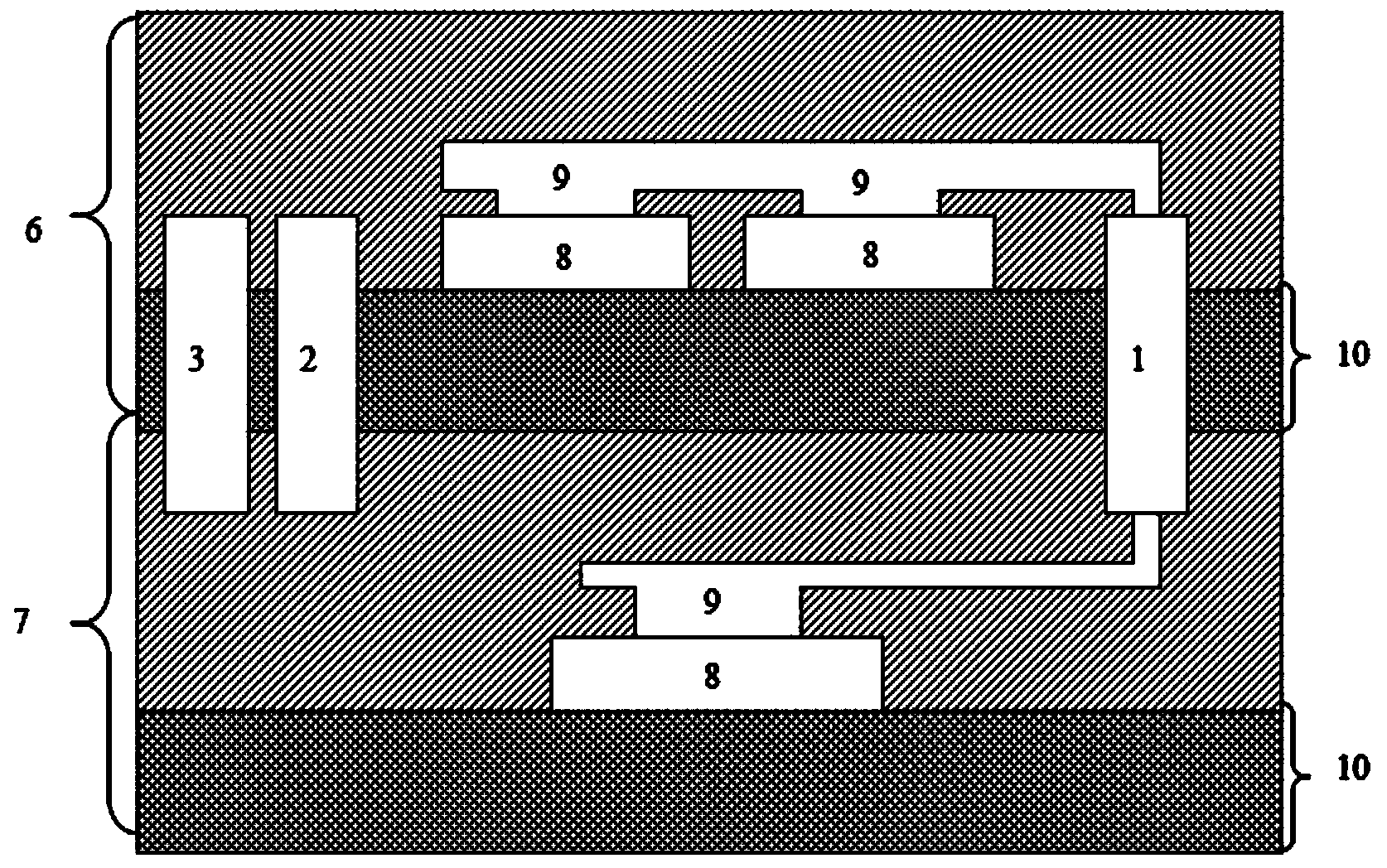

[0043] Such as figure 1 Shown is a schematic cross-sectional view of a 3D integrated circuit chip. The 3D integrated circuit in the present invention is a three-dimensional chip structure. figure 1 Among them, 1 is signal TSV, 2 is thermal via a, 3 is thermal via b, 6 is the top chip, 7 is the bottom chip, 8 is the chip standard unit, 9 is the metal connection layer, and 10 is the silicon substrate.

[0044] Each layer in the 3D chip is a 2D chip, and is connected vertically by the TSV shown in 1, which includes the top chip 6 and the low layer chip 7; the standard unit 8 is the basic component for realizing signal interconnection in the integrated circuit, Each standard unit 8 is interconnected through metal interconnection lines 9; the top chip 6 and the bottom chip 6 need to be connected through 1, 1. This TSV is a through-silicon hole passing through two adjacen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More