Embedded germanium-silicon epitaxy dislocation fault improving method

An embedded germanium-silicon, dislocation technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as interface defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

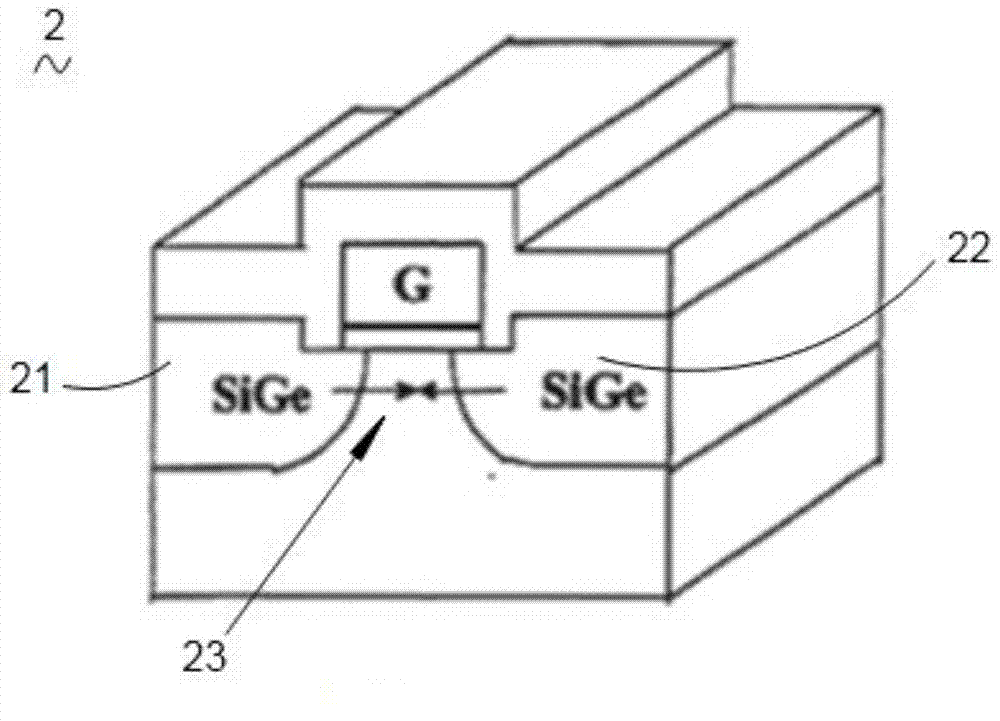

[0018] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

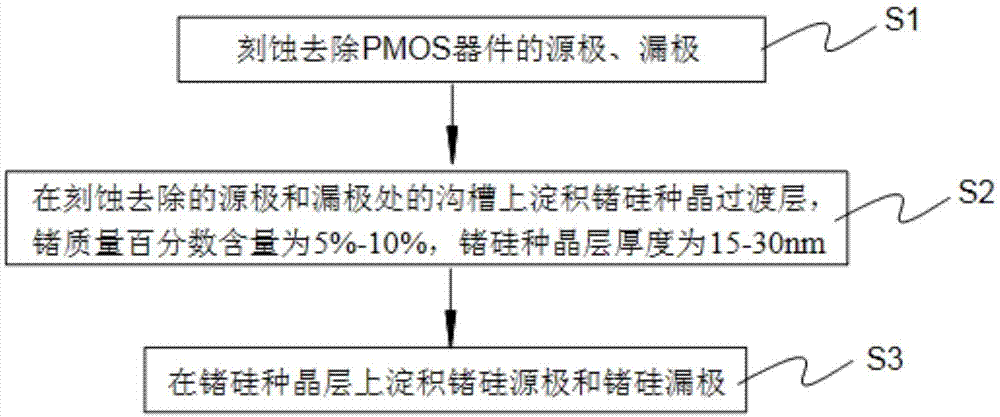

[0019] see figure 1 , figure 1 Shown is a flow chart of the method for improving dislocation defects in embedded silicon germanium epitaxy according to the present invention. The method for improving the embedded silicon germanium epitaxial dislocation defect comprises the following steps,

[0020] Executing step S1: removing the first source and the first drain of the first PMOS device 1 by etching;

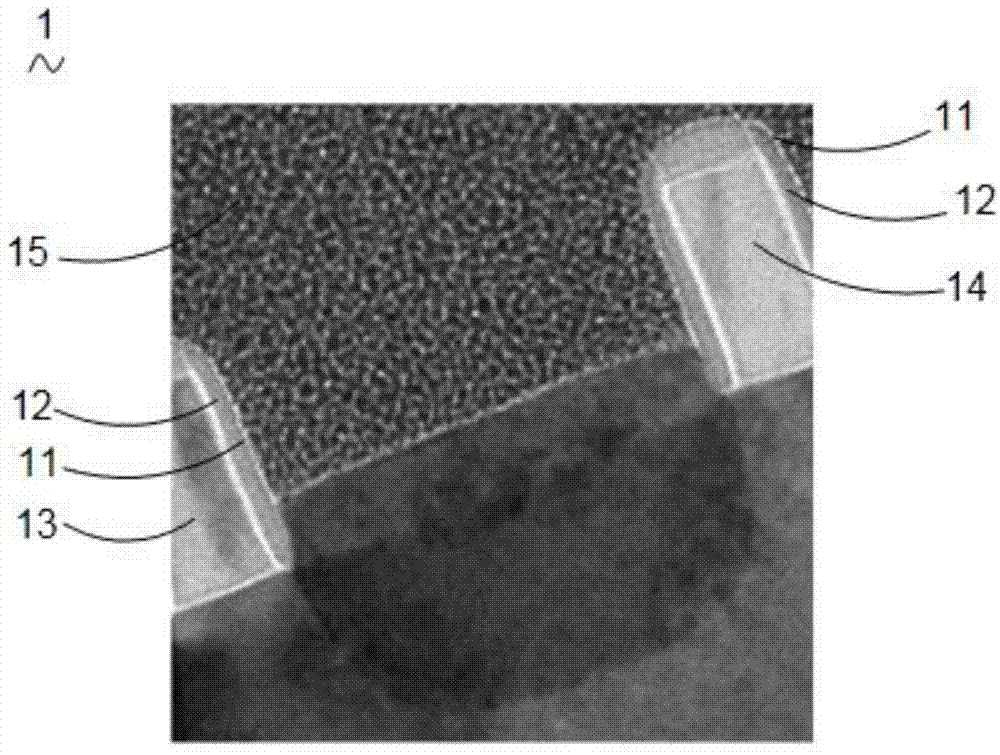

[0021] Executing step S2: depositing a germanium-silicon seed crystal transition layer 12 on the groove 11 at the first source and the first drain removed by etching, and the germanium-silicon seed transition layer 12 has a quality of germanium The percentage content is 5% to 10%, and the film thickness of the silicon germanium seed t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Film thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More