AES parallel implementation method based on OpenCL

An implementation method and round key technology, which is applied in the field of rapid implementation of AES, can solve the problems of not having a high degree of parallel structure, delay, and parallel capability inferior to GPU, etc., to achieve easy implementation, improved cracking efficiency, and high cost performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

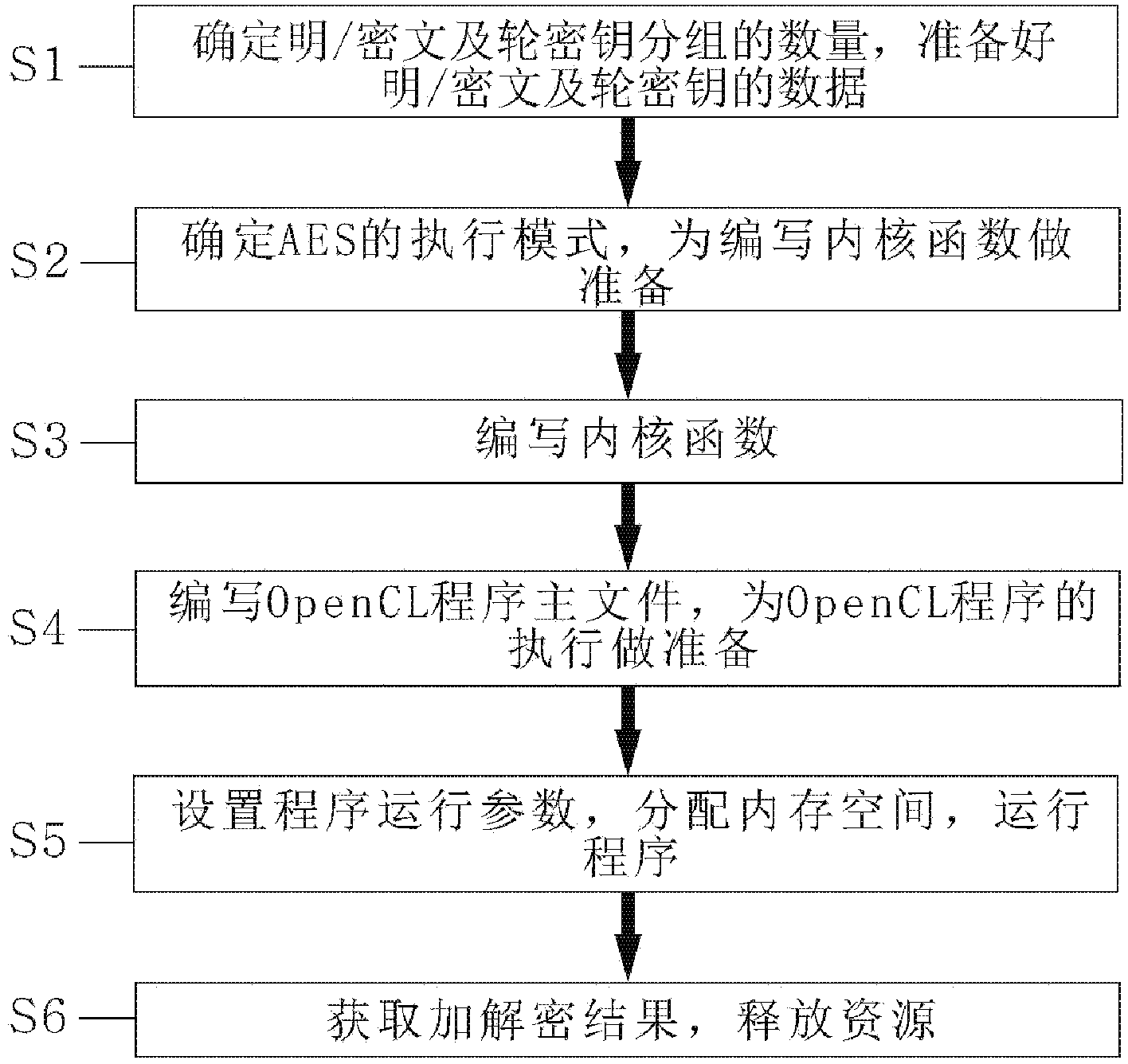

[0044] This embodiment provides an implementation method of AES parallel encryption based on OpenCL. According to the steps of this embodiment, a slight modification can also be used to implement parallelized decryption or parallelized encryption and decryption.

[0045] Such as image 3 Shown, the AES parallelization realization method based on OpenCL of the present invention comprises the following steps:

[0046] S1. Determine the number of plain / ciphertext and round key groups, and prepare the data of plain / ciphertext and round key;

[0047] S2. Determine the execution mode of AES to prepare for writing the kernel function;

[0048] S3, write the kernel function;

[0049] S4, write the main file of the OpenCL program to prepare for the execution of the OpenCL program;

[0050] S5, setting program operation parameters, allocating memory space, and running the program;

[0051] S6. Obtain an encryption and decryption result, and release resources.

[0052] The above st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More