Integrated passive device wafer-level packaging three-dimensional stacked structure and manufacturing method

A technology for integrating passive devices and wafer-level packaging, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as low integration and non-integration of passive passive devices, and achieve good stress buffering Protective effect, improve electrical quality, and improve cost performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with specific drawings.

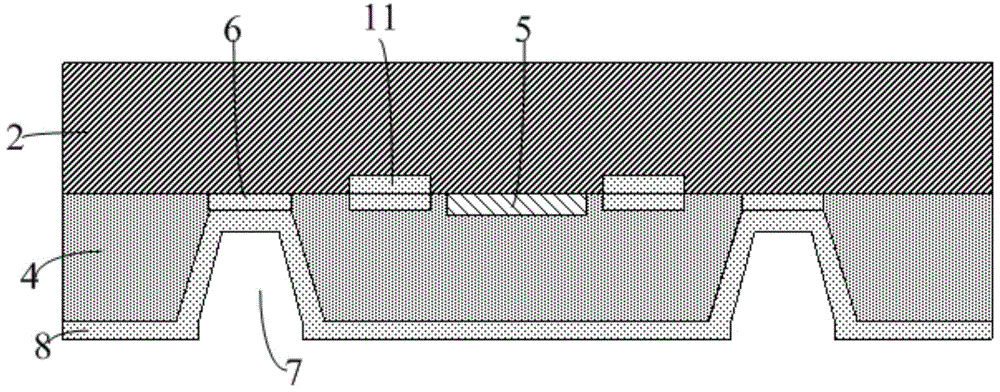

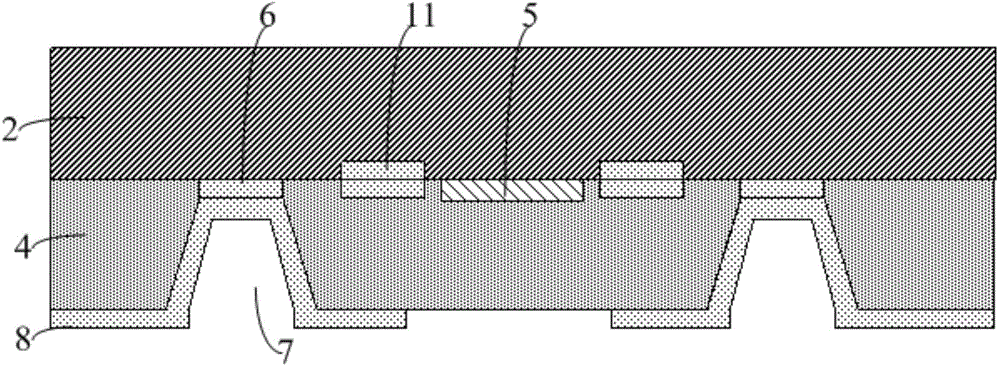

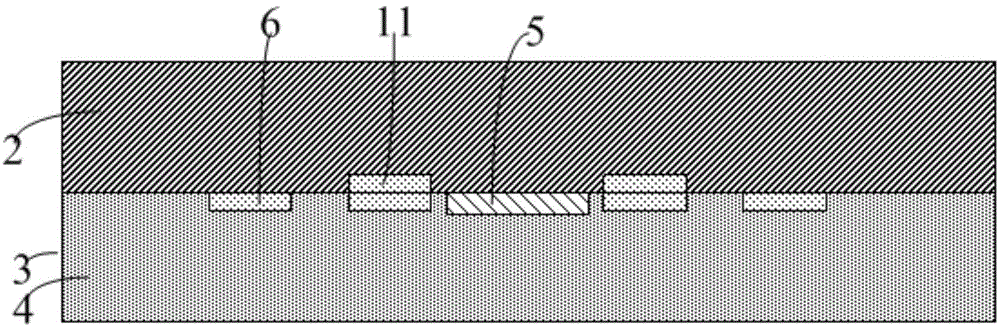

[0025] Such as Image 6 As shown: the integrated passive device wafer level package three-dimensional stack structure includes PCB board 1, wafer level package chip 2, IPD chip 3, glass substrate 4, IPD device 5, metal wiring layer 6, TGV hole 7, back Metal wiring layer 8, pad 9, solder ball 10, chip signal port 11, etc.

[0026] Such as Image 6 As shown, the three-dimensional stacked structure of the present invention is packaged on a PCB board 1, including a wafer-level packaging chip 2 and an IPD chip 3; the IPD chip 3 includes a glass substrate 4, and an IPD device 5 and Connect the metal wiring layer 6 of the IPD device 5, the IPD device 5 and the metal wiring layer 6 are flush with the front of the IPD chip 1, and the metal wiring layer 6 is connected to the chip signal port 11 of the wafer-level packaging chip 2; on the glass substrate The backside of 4 is etched to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More