Method for manufacturing fin field effect transistor

A technology of fin field effect and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as unfavorable oxide filling, reducing device stability, etc., so as to improve device performance and increase filling process. effect of windows, improved process efficiency and etch accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the purpose and features of the present invention more obvious and easy to understand, the following will further describe the specific embodiments of the present invention in conjunction with the accompanying drawings. However, the present invention can be realized in different forms, and should not be considered as being limited to the described embodiments .

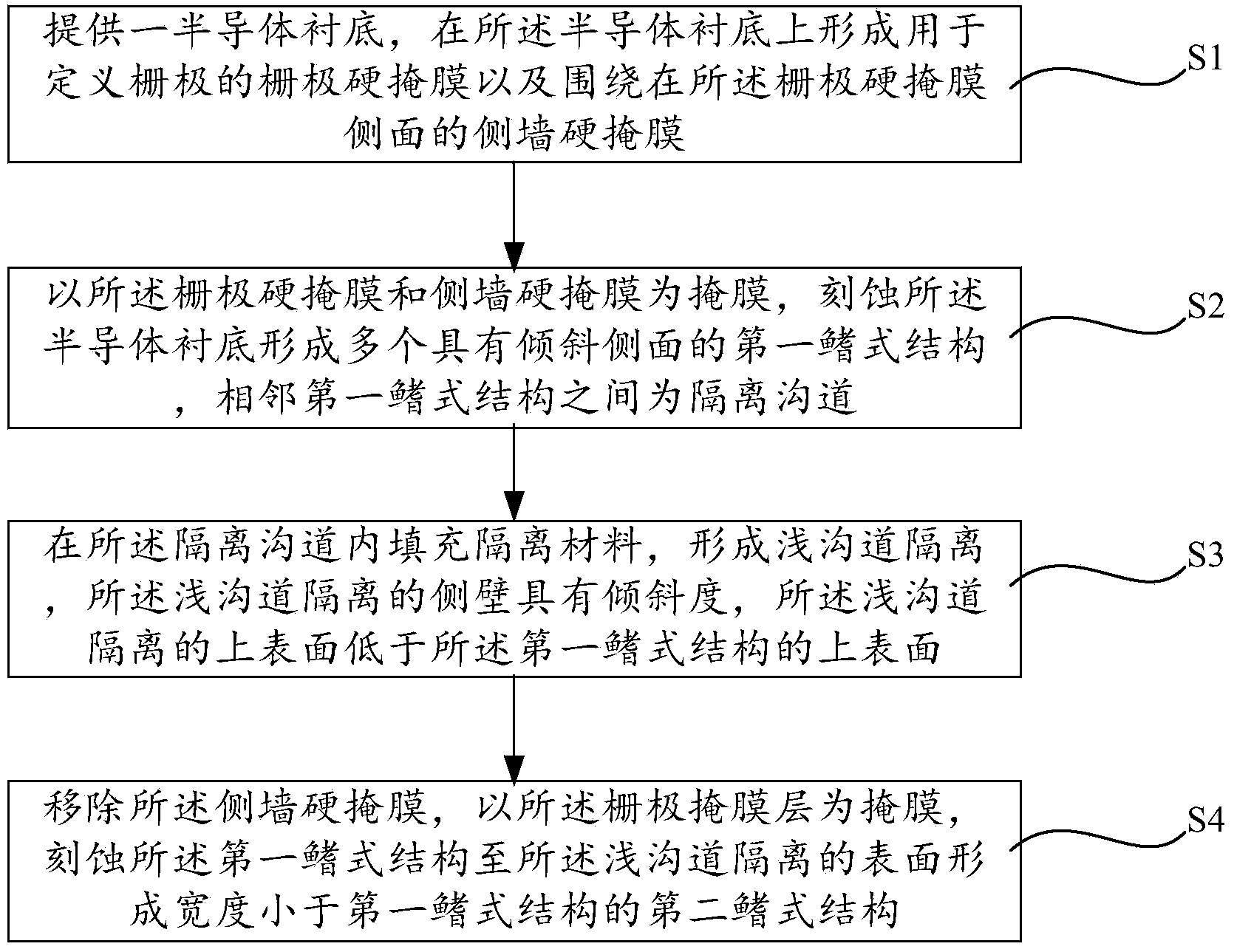

[0030] Please refer to figure 2 , the present embodiment provides a method for manufacturing a fin field effect transistor, including:

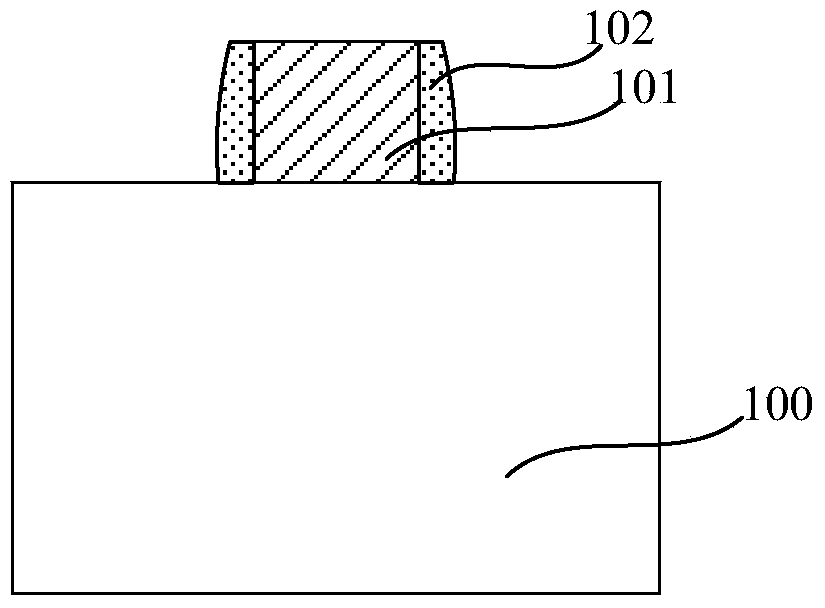

[0031] S1, providing a semiconductor substrate, forming a gate hard mask for defining a gate and a sidewall hard mask surrounding the sides of the gate hard mask on the semiconductor substrate;

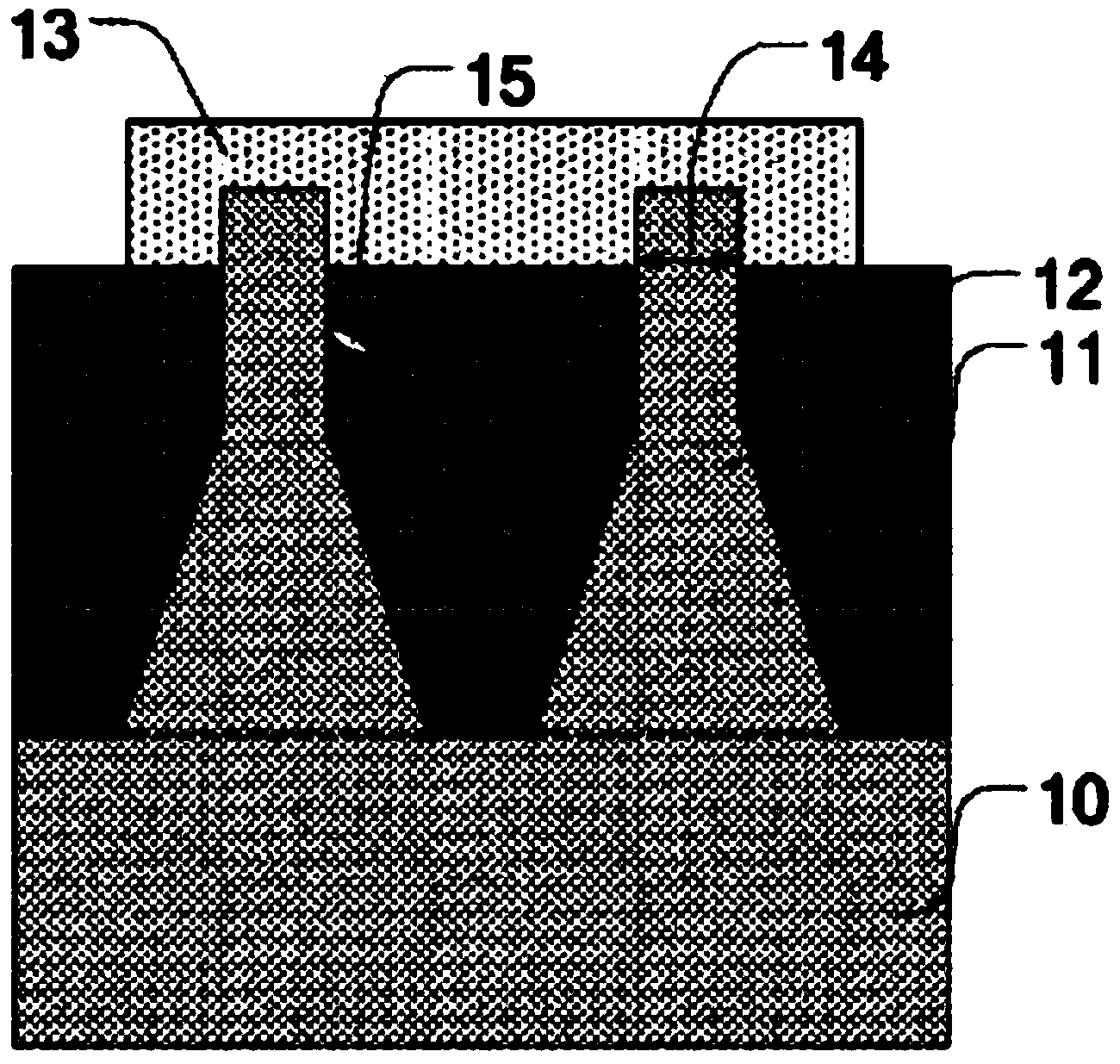

[0032] S2, using the gate hard mask and the sidewall hard mask as a mask, etch the semiconductor substrate to form a plurality of first fin structures with inclined sides, and between adjacent first fin structures is isolation trench;

[0033] S3, filling the isol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More