Chip-stacking encapsulation structure and electronic equipment

A technology of chip stacking and packaging structure, applied in the field of electronics, can solve problems such as difficulty in wiring, and achieve the effects of reducing wiring space resources, improving performance, and improving resource utilization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

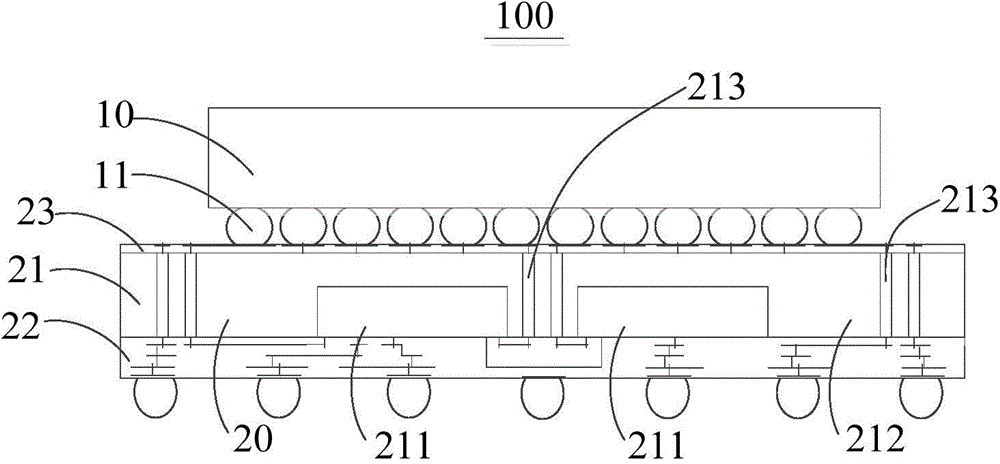

[0029] Such as figure 1 As shown, it is a schematic structural diagram of a chip stack package structure 100 provided by a preferred embodiment of the present application. The chip stack package structure 100 includes a first chip 10 and a second chip 20 .

[0030] The first chip 10 may be a memory chip (Memory), a silicon grain (Silicon Die), a flip-chip package structure (Flip Chip Package), a passive device (Passive Device), etc., or may be an integrated single or multiple chip Die fan-out wafer level packaging. Solder balls 11 are disposed on the first chip 10 , and the first chip 10 can be electrically connected with other electronic components through the solder balls 11 . The solder ball 11 may be a solder ball (Solder Ball), a solder bump (Solder Bump) or a copper pillar (Cu Pillar).

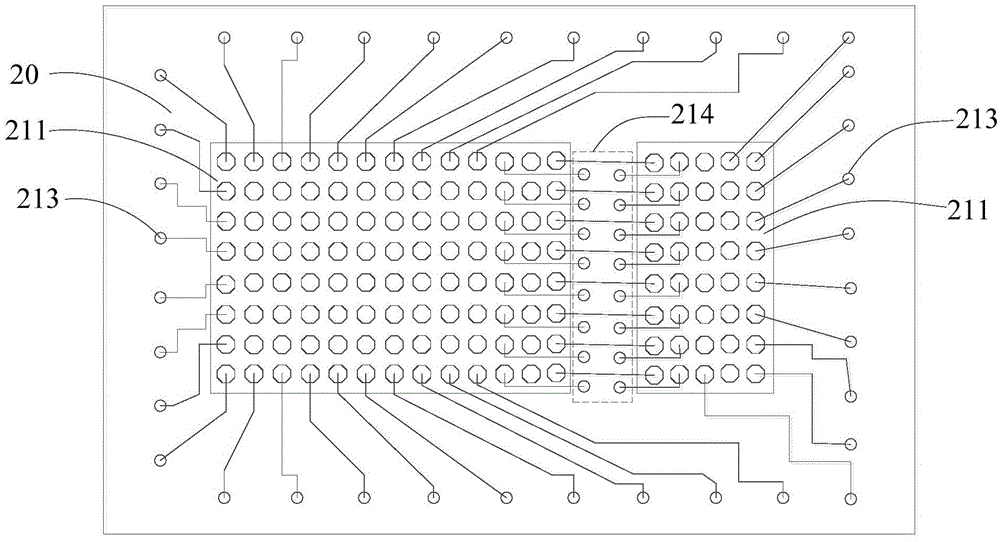

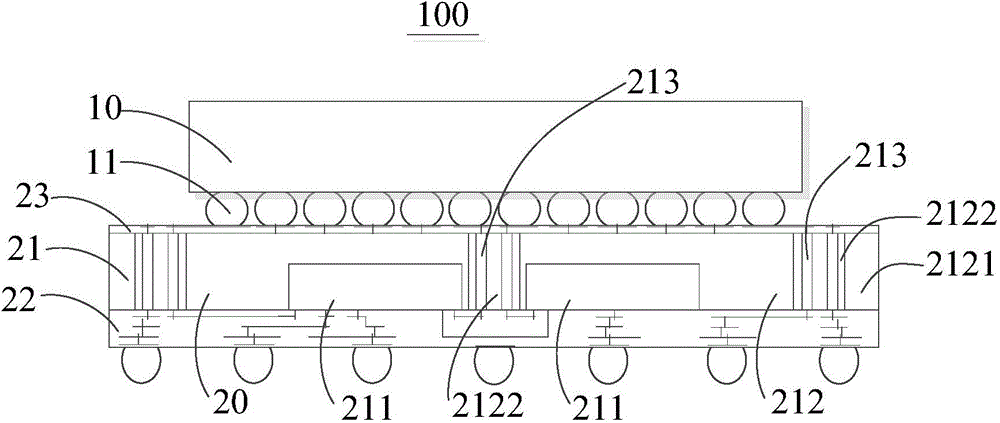

[0031] see also figure 2 , the second chip 20 and the first chip 10 are stacked and fixed to each other. The structure of the second chip 20 is the same as that of the first chip 1...

Embodiment 2

[0047] Based on the same inventive concept, the present application also provides an electronic device. Such as Figure 5 As shown, is a schematic structural diagram of the electronic device 200 of the present application. The electronic device 200 includes a circuit board 210 and a chip stack package structure 220 disposed on the circuit board. The structure and function of the chip stack package structure 220 are the same as those of the chip stack package structure 100 in the first embodiment, and will not be repeated here. The second chip 20 of the chip stack package structure 220 is located between the first chip 10 and the circuit board 210 .

[0048] The above-mentioned electronic device 200 adopts the chip stacking package structure 220, and adds a through hole 213 between at least two dies 211 of the second chip 20, so that the fan-out input and output lines on the die 211 can be directly passed through. The through hole 213 around the crystal grain 211 is electric...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More